to be triggered by other conditions such as Live Line/Dead Bus. If Dead Time Enabled is not mapped in PSL, it

defaults to high, so the dead time can r

un.

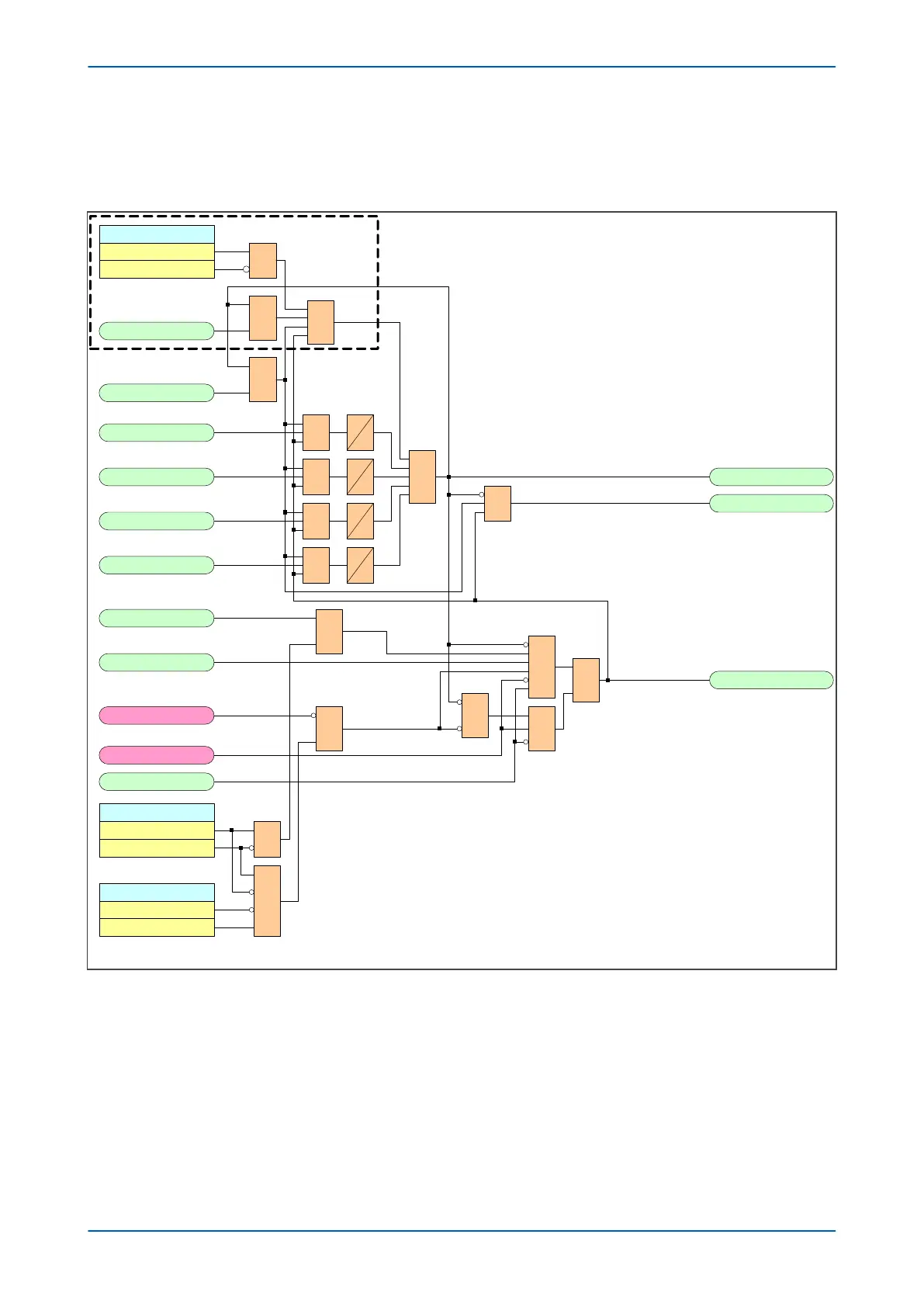

The dead time control logic is shown below.

DT Complete

AR with ChkSyn

Disable

Enable

V00508

&

AR Sync Check

DeadTime Enabled

AR SeqCounter 4

AR SeqCounter 3

AR SeqCounter 2

AR SeqCounter 1

1

1

&

&

&

&

&

1

&

Reclose Checks

DeadTime in Prog

S

R

Q

CB Open 3 ph

DT OK To Start

Autoreclose Start

Autoreclose Initiate

AR In Progress

Sequence Co -ord

Disable

Enable

1

Start Dead t On

CB Trips

Protection Reset

&

&

1

&

&

1

Scheme 2 (Voltage models only )

Figure 154: Dead Time Control logic

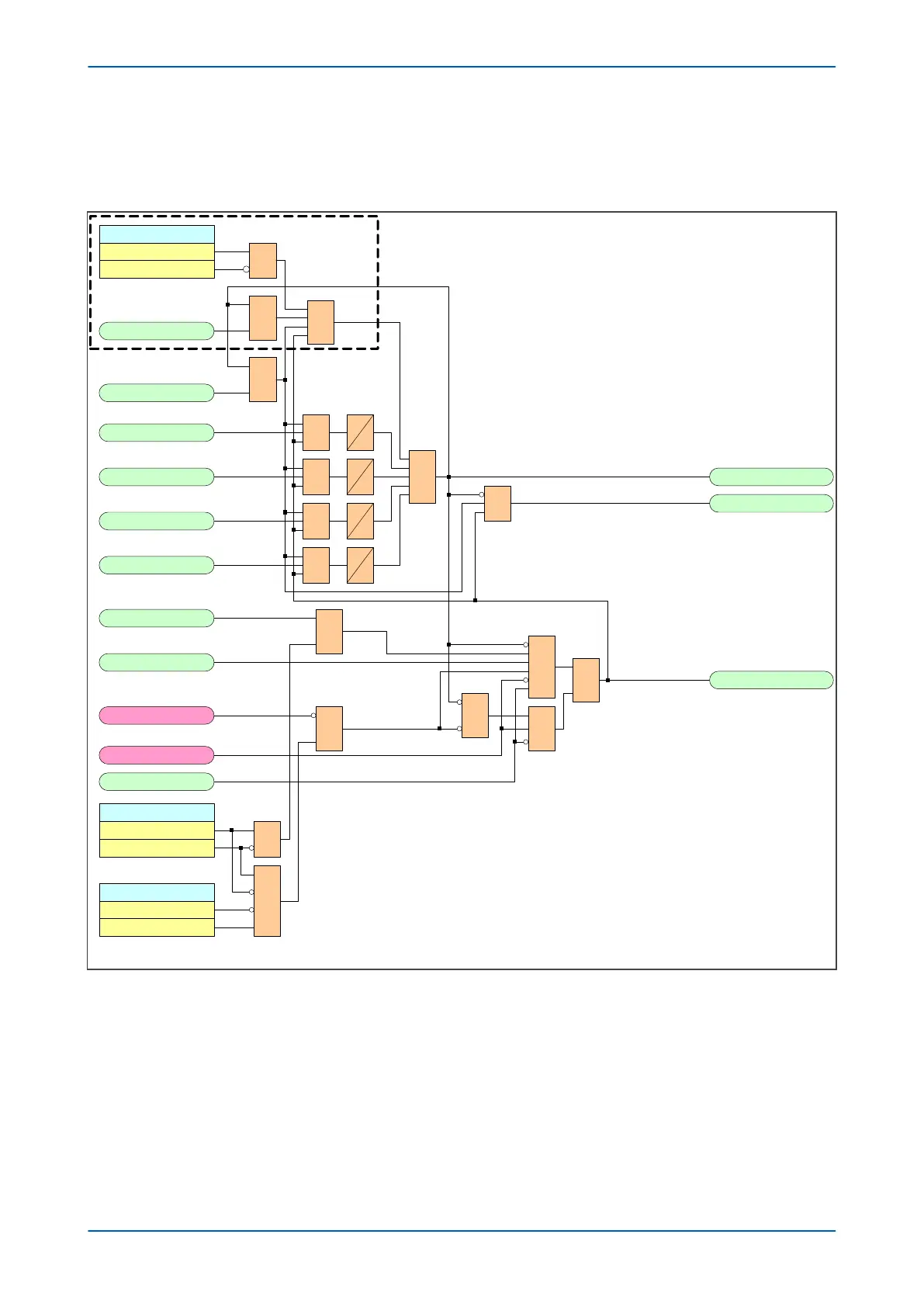

7.5.1 AR CB CLOSE CONTROL

Once the dead time is completed or a synchronism check is confirmed, the Aut

o Close signal is given, provided

both the CB Healthy and the System Checks are satisfied. The Auto Close signal triggers a CB Close command via

the CB Control functionality.

The AR CB Close Control Logic is as follows:

P14x Chapter 13 - Autoreclose

P14xEd1-TM-EN-1 297

Loading...

Loading...