Function block library

7-182

SHB9300CRV EN 2.0

7.6.58 Actual phase integrator (PHDIFF)

Purpose

Deliberate addition of a phase signal to the setpoint phase.

A comparison between setpoint and actual phase signals is also possible.

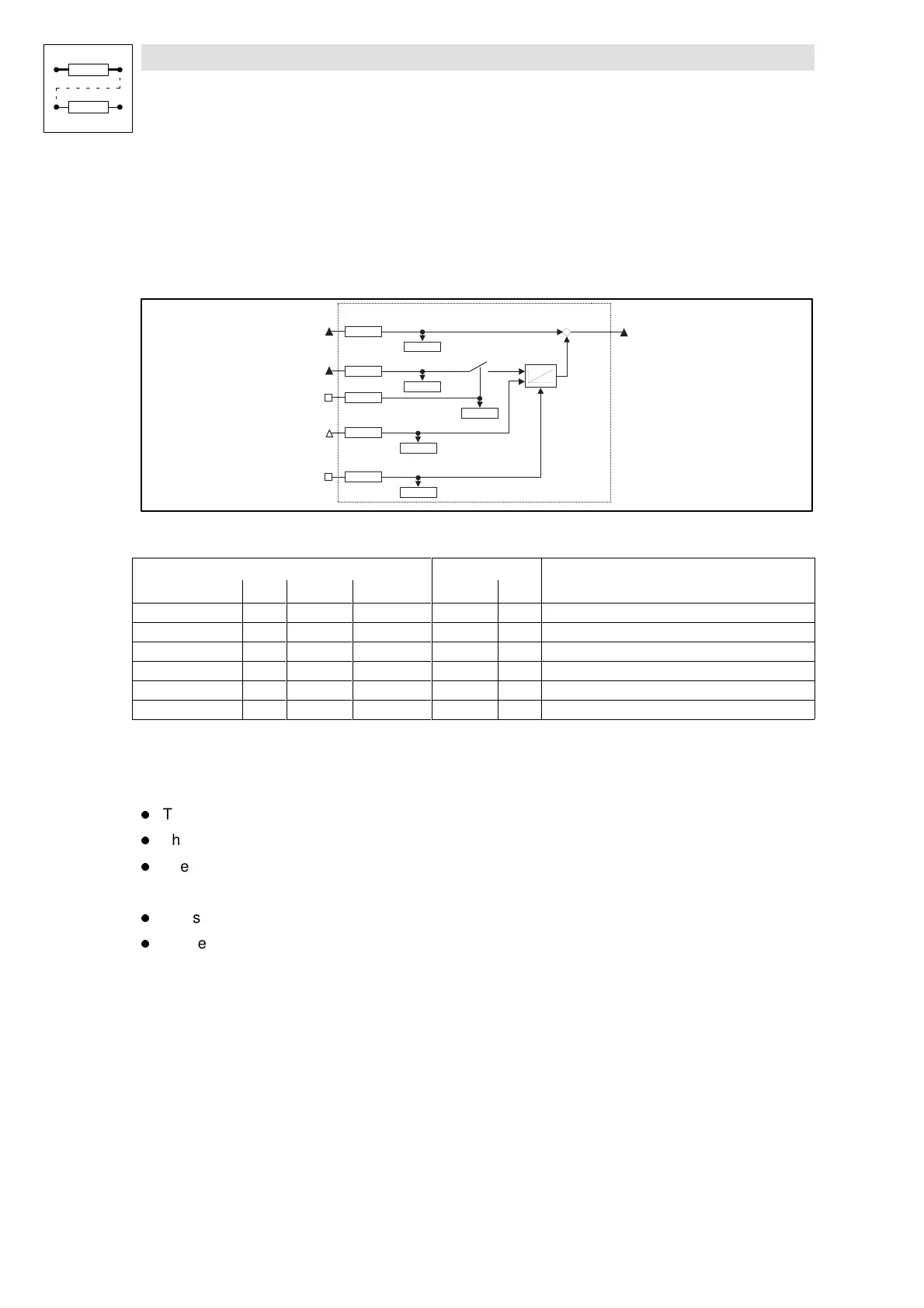

PHDIFF1

PHDIFF1-OUT

PHDIFF1-ADD

C 1237/2

C 1232/2

PHDIFF1-SET

C 1237/1

C 1232/1

PHDIFF1-IN

C 1236

C 1231

C 1230/1

C 1235/1

PHDIFF1-EN

C 1230/2

C 1235/2

PHDIFF1-RESET

+

-

Fig. 7-146 Actual phase integrator (PHDIFF1)

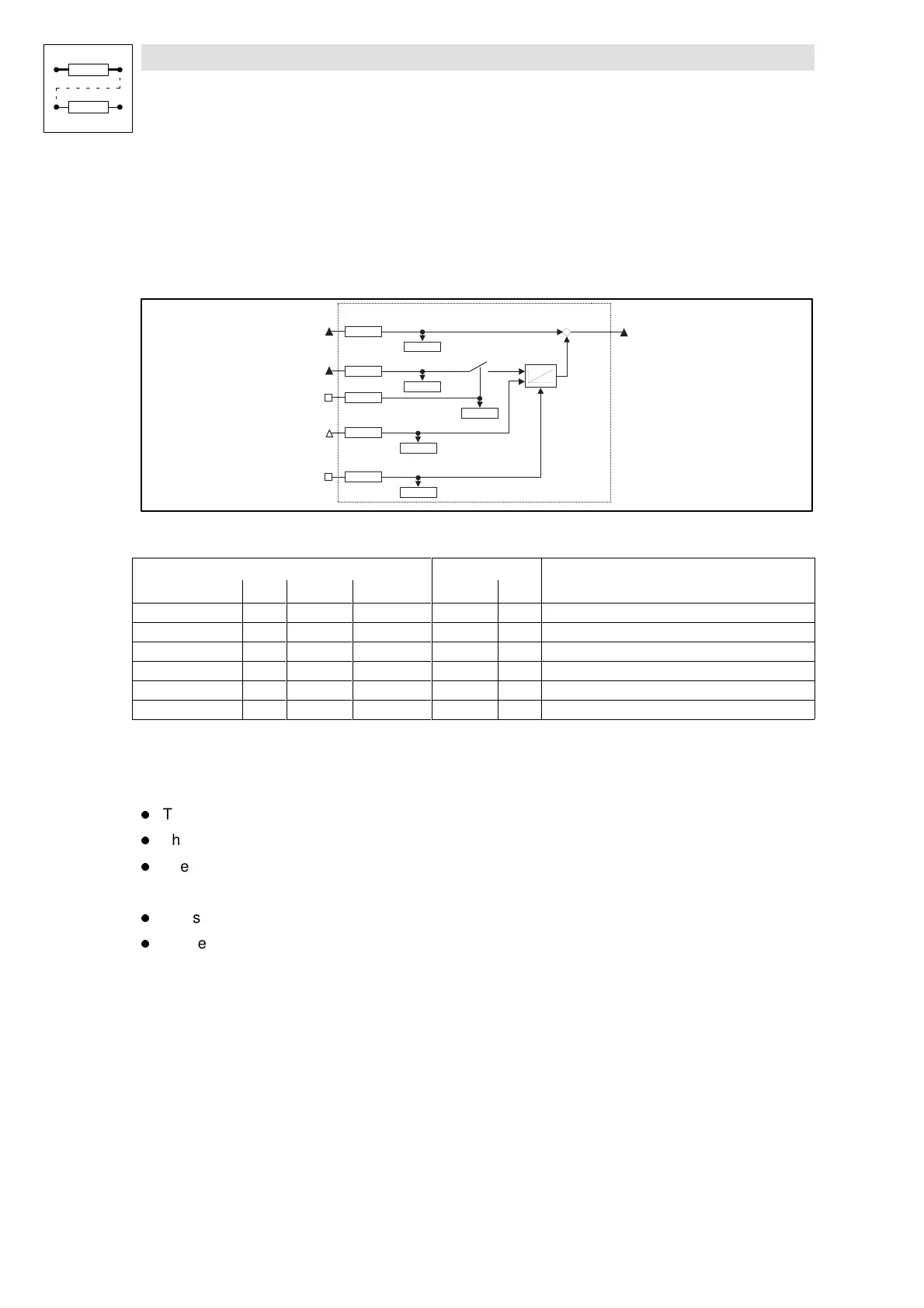

Signal

Source Note

Name Type DIS DIS format CFG List

PHDIFF1-IN phd C1236 dec [rpm] C1231 4 -

PHDIFF1-SET ph C1237/1 dec [inc] C1232/1 3 -

PHDIFF1-ADD ph C1237/2 dec [inc] C1232/2 3 -

PHDIFF1-EN d C1235/1 bin C1230/1 2 -

PHDIFF1-RESET d C1235/2 bin C1230/2 2 HIGH = sets the actual phase integrator = 0

PHDIFF1-OUT ph - - - - without limitation

Function

C1230/1 = HIGH

l

The speed signal at PHDIFF1-IN is integrated by the actual phase integrator.

l

The phase signal at PHDIFF1-ADD is integrated to the integrated speed signal.

l

The result of the actual phase integrator is subtracted from the phase signal at PHDIFF1-SET.

C1230/1 = LOW

l

The speed signal at PHDIFF1-IN is integrated by the actual phase integrator.

l

The result of the actual phase integrator is subtracted from the phase signal at PHDIFF1-SET.

Loading...

Loading...