Function block library

7-217

SHB9300CRV EN 2.0

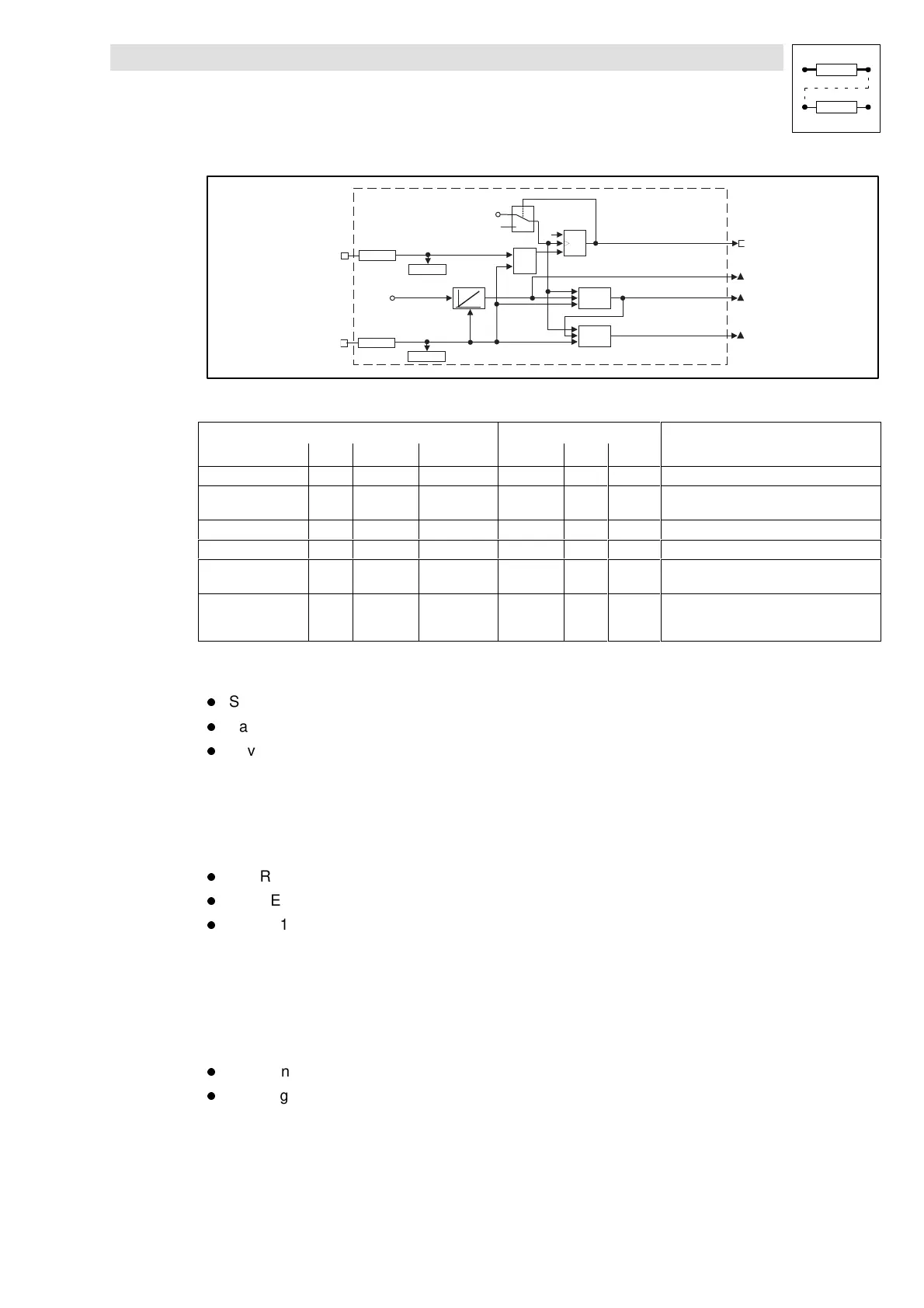

C 1223/1

STORE2-RESET

C 1220/1

C 1223/2

STORE2-ENTP

C 1220/2

> 1

_

R

D

1

1

0

TP Eingang E4

0

Reg1

R

C

Reg2

R

C

STORE2-PH1

STORE2-PH2

STORE2-ACT

STORE2-TP-INH

STORE2

MCTRL-PHI-ACT

Fig. 7-179 Memory block (STORE2)

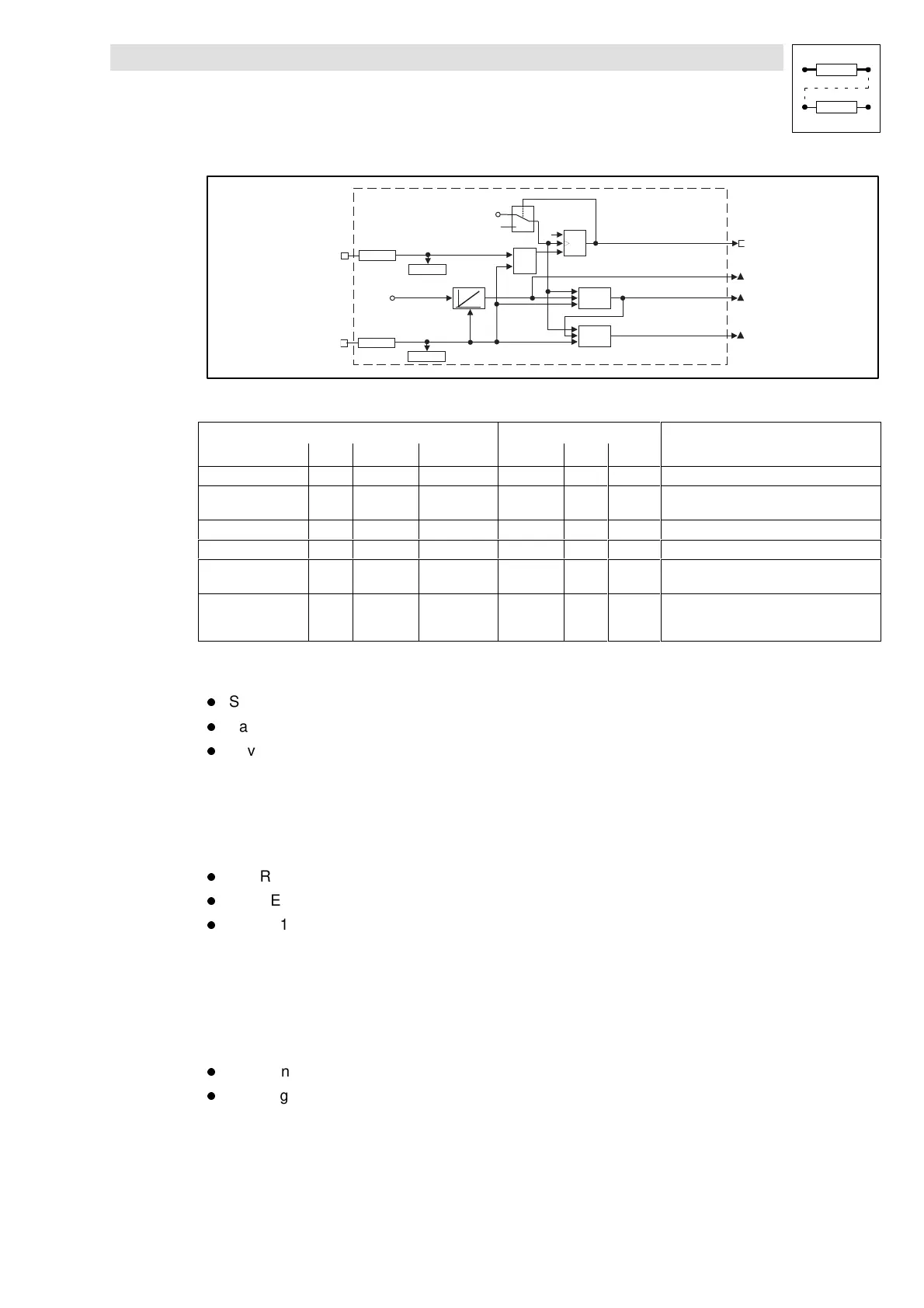

Signal

Source Note

Name Type DIS DIS format CFG List Lenze

STORE2-RESET d C1223/1 bin C1220/1 2 1000 HIGH = resets all functions

STORE2-ENTP d C1223/2 bin C1220/2 2 1000 HIGH = enables the triggering via the

TP input E4

STORE2-ACT ph - - - - - Outputs the current, integrated value

STORE2-PH1 ph - - - - - Outputs the last value stored by X5/E5

STORE2-PH2 ph - - - - - Outputs the last but one value stored by

X5/E5

STORE2-TP-INH d - - - - - HIGH = Triggering via TP input E4 was carried

out. For another triggering, a positive edge

must occur at the input STORE-ENTP.

Function

l

STORE1 control via TP input E5

l

Save STORE1 phase signal

l

Save STORE2 phase signal

7.6.72.1 STORE1 control via TP input E5

The trigger signal STORE1-TP-INH indicates a triggering with a HIGH signal via the TP input E5

(LOW-HIGH edge at X5/E5). The STORE1-TP-INH signalizes at the time that the triggering is

deactivated and must be reset to the active state. This can be done by

l

STORE1-RESET = HIGH

l

STORE1-ENTP = LOW-HIGH edge

l

STORE1-ENWIN = HIGH and the comparison of phase signals

Comparison of phase signals

The speed signal at STORE1-MASKI is integrated to a phase signal and compared with the phase

signal at STORE1-MASKV.

If the condition | STORE1-MASKI | STORE1-MASKV

is fulfilled,

l

the TP input E5 for the next triggering is enabled with STORE1-ENWIN = HIGH,

l

the integrator for the speed signal at STORE1-MASKI is reset.

7.6.72.2 Save STORE1 phase signal

A speed signal at input STORE1-IN is added to a phasesignal. Thefollowing sequence indicates the

ways of signal output and storage.

Loading...

Loading...