Function block library

7-118

SHB9300CRV EN 2.0

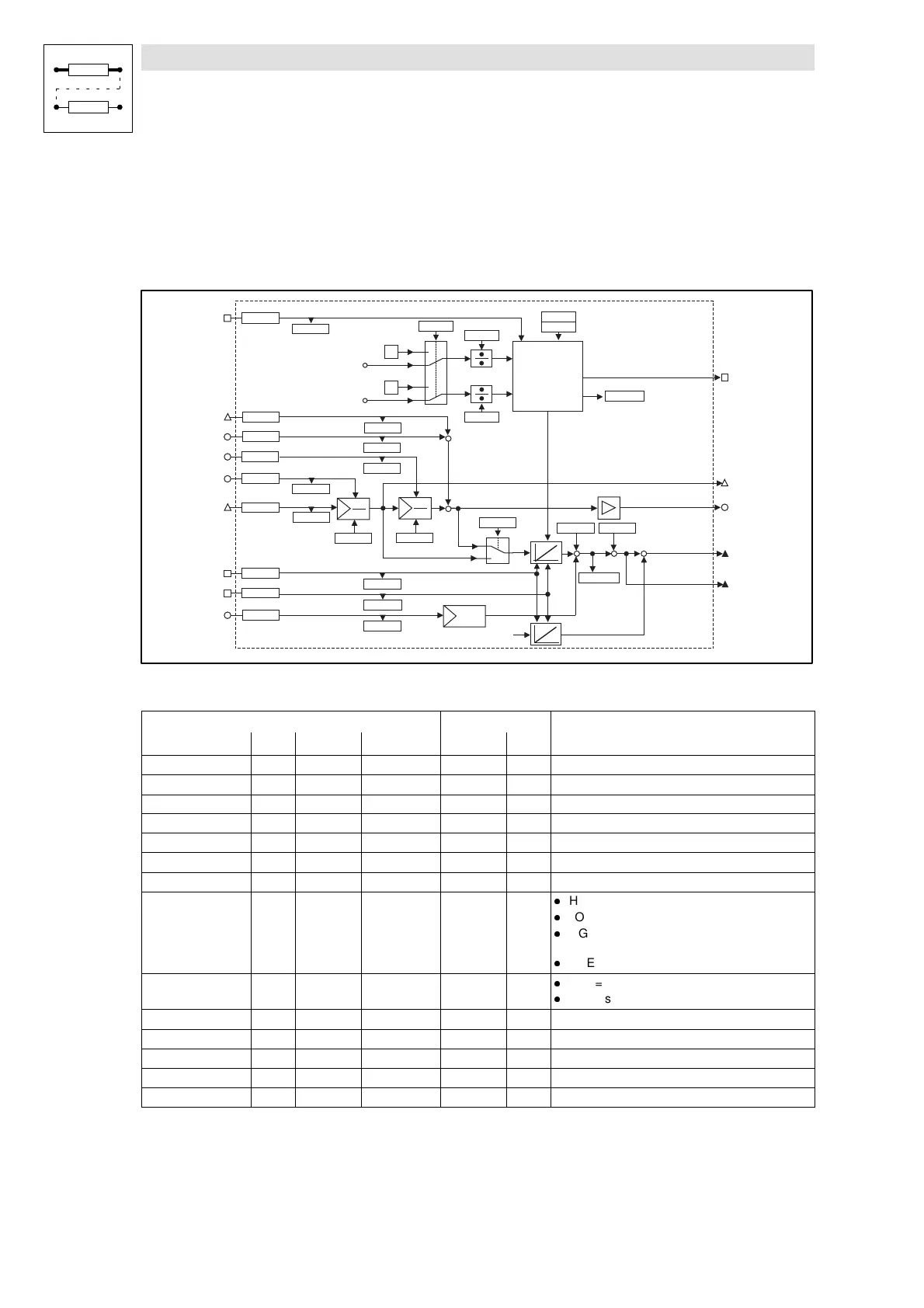

7.6.34 Digital frequency processing (DFSET)

Purpose

Conditions the digital frequency for the controller. Input of the stretch factor, gearbox factor and the

speed or phase trimming.

*

a

b

b

a

*

a

b

b

a

+

+

1

0

+

+

C 0537

C 0536/2

C 0536/1

C 0033

C 0533

C 0530

C 0252

C 0536/3

C 0538/2

C 0539

DFSET

DFSET-NOUT

+

-

DFSET-A-TRIM

DFSET-N-TRIM

D F S E T -R A T -D IV

DFSET-RESET

DFSET-IN

DFSET-PSET

DFSET-VP-DIV

DFSET-PO UT

DFSET-SET

C 0538/3

+

+

C 0253

C 0531

C 0535

C 0532

2

1

2

1

E4

E5

X5

X5

X9/6,7

MCTRL-PHI-ACT

C 0538/1

DFSET-0-PULSE

DFSET-ACK

C 0525

C 0522

C 0524

C 0521

C 0520

C 0527

C 0526

C 0523

C 0534

*

C 0529

C 0528/1

C 0528/2

CTRL

DFSET-PSET2

C 1258

DFSET-N-TRIM2

C 1255

+

+

C 0429

Fig. 7-86 Digital frequency processing (DFSET)

Signal

Source Note

Name Type DIS DIS format CFG List

DFSET-IN phd C0539 dec [rpm] C0520 4 Speed/Phase setpoint

DFSET-N-TRIM a C0537 dec [%] C0524 1 Speed trimming in [%] of C0011

DFSET-N-TRIM2 phd C1258 dec [rpm] C1255 4 Speed trimming in [rpm] of C0011

DFSET-A-TRIM a C0536/3 dec [inc] C0523 1 Phase trimming 100% = 16384 inc

DFSET-VP-DIV a C0536/1 dec C0521 1 Numerator stretch factor 100 % = 16384 inc

DFSET-RAT-DIV a C0536//2 dec C0522 1 Numerator gearbox factor 100 % = 16384 inc

DFSET-0-PULSE d C0538/1 bin C0525 2 HIGH = Enabling of zero pulse synchronizing

DFSET-SET d C0538/3 bin C0527 2

l

HIGH = Set phase integrators to equal values

l

LOW-HIGH edge sets DFSET-PSET = 0

l

HIGH-LOW edge sets DFSET-PSET = momentary

value of MCTRL-PHI-SET

l

DFSET-SET has a higher priority than DFSET-RESET

DFSET-RESET d C0538/2 bin C0526 2

l

HIGH = sets position difference = 0

l

HIGH = sets DFSET-PSET and DFSET-PSET2 = 0

DFSET-NOUT a - - - - in [%] of nmax (C0011)

DFSET-POUT phd - - - - Speed/Phase setpoint

DFSET-PSET ph - - - - Contouring error for phase controller

DFSET-PSET2 ph - - - - Phase setpoint 65536 inc = 1 revolution

DFSET-ACK d - - - - HIGH = Synchronizing is performed

Loading...

Loading...