When

the

CCP/SCSR switch is in

the

CCP position and

switch 0 is in the

'rOil

position, switches 3 through 7

specify

the

binary address of

the

cabinet

whose

Read

Direct

Mode 9 Status Register is to be displayed by the 32 panel

indicators.

When

the

CCP/SCSR switch

IS

In

the CCP position and

switch 0 is in the

11111

position, switches 3 through 7 specify

the binary address of

the

cabinet

whose

16-bit

Configura-

tion Status Register is to be displayed by

the

16 lower-order

indicators.

SINGLE CLOCK

ENABLE

This switch stops all

central

system clocks in

the

same

manner as the

ZCCLK

command. Activating this switch

when

the

basic processor

is

performing normal

data

processing

may have an adverse effect on any

active

I/O

operations.

To

prevent inadvertent

activation

of this

control,

it

is

disabled unless the MAINT MODE switch is in

the

ON

position.

SINGLE CLOCK

STEP

This switch is

active

only when in Single Clock Mode or

when the Single Clock Enable switch is

active.

When

active,

this switch causes one system

clock

to be issued

each

time

it

is

placed

in the

STEP

position. The new

single

clock

status, as

selected

by

the

MODE and

SELECT

switches, may .be monitored

via

the

32 binary indicators

C~

the Sy!te!!!

Cc~t!"c!

P(!~e!;

~~

~:H!:p!(!y

;!:

ge~er~ted

0~

thE'

System Control Console

by

activation

of the SCP Single

Clock Step switch.

OPERATING

PROCEDURES

AND

INFORMATION

This section contains reference information which

may

be

required by either the operator or maintenance/diagnostic

personnel.

LOAD

OPERA

nON

DETAILS

The first

executed

instruction of

the

bootstrap program

{in

location X'26'} loads general register 0 with

the

address of

the

first

I/O

command doubleword (IOCD). The

I/o

address

for the SIO instruction in location

X'27'

is the

13

low-order

bits of location

X'25'

{which have been set equal to the load

unit address

asa

result of the NORMAL LOAD,

ZCLDN"",

command}. During execution of the SIO instruction,

gen-

eral register 0 points to locations

X'20'

and

X'21'

as

the

first IOCD for

the

selected

device.

This IOCD contains

an

order

to

the

selected peripheral

device

to read 88 (X'58')

bytes of

data

into consecutive memory locations beginning

at

word location X'2A' (byte location X'A8'). At

the

end

of

the

Read operation,

neither

data

chaining

nor command

chaining is

called

for in

the

10CD.

The Suppress Incorrect

Length

(SIL)

flag is set to 1 so

that

an

incorrect length

in-

dication

will not

cause

a Transmission Error Halt. After

the

SIO

instruction has been

executed,

the

basic processor

executes

a

no

instruction with

the

same

effective

addressas

the

SIO

instruction. The

no

instruction is coded

to

accept

only

condition

code

data

from

the

lOP.

The

BCS

instruction (in

location

X'29')

will

cause

a branch

to

X'22'

(a

LOAD

IMMEDIATE

instruction), if

either

CC1

or CC2 is set

to

1.

Execution of the

LOAD

IMMEDIATE

instruction

at

X'22'

loads a count of X'10029' into general register

1.

The

fol-

lowing

BDR

instruction

at

location

X'23'

uses this as a

"delay"

count

before executing

the

BCR

instruction in

lo-

cation

X'24',

which unconditionally branches

to

the

no

instruction in location

X'28'.

In normal operations,

CC1

is

reset

to

0 and CC2 remai

ns

set

to

1 unti I

the

device

can

accept

another SIO instruction. At

that

time, the next

instruction is taken from

location

X'2A'.

If

a Transmission Error or equipment malfunction is

detected

by

either

the

device

or

the

lOP,

the

lOP

instructs

the

d,evice to

halt

and to

initiate

an

II

unusual end" interrupt

signal (as specified by appropriate flags in the

IOCD,

de-

scribed in Chapter 4). The

II

unusual end" interrupt will

be

ignored since all interrupt levels have been Disarmed

and

Disabled by the system reset during

the

load sequence.

The

device

wi

II

not

accept

another SIO while

the

interrupt

is pending and

the

BCS

instruction in location

X'29'

will

continue

to branch to location

X'22'.

The

correct

operator

action

at

this point is to

repeat

the

NORMAL LOAD,

ZCLDN####, command. If

there

is no

I/O

address

recog-

nition of the load unit,

the

SIO

instruction will not

cause

any

I/O

action

and

CC1

will

continue

to

be set to 1 by

the

$iO

and

no instructions causing

the

BCS

instruction to

branch.

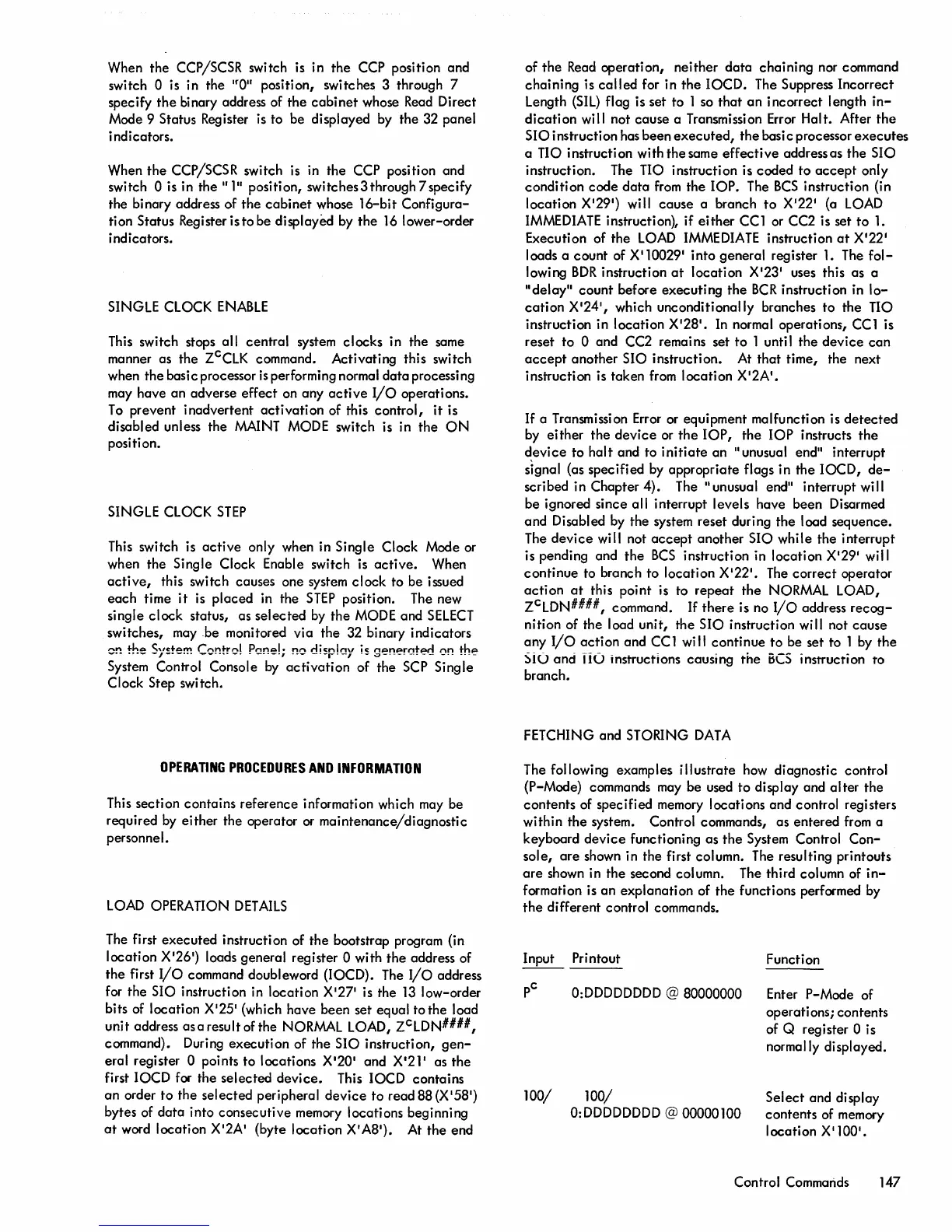

FETCHING and STORING

DATA

The following examples illustrate how diagnostic control

(P-Mode) commands may be used

to

display and

alter

the

contents of specified memory locations and control registers

within

the

system. Control commands, as entered from a

keyboard

device

functioning as

the

System Control

Con-

sole,

are

shown in the first column. The resulting printouts

are

shown in

the

second column. The third column of

in-

formation is

an

explanation of

the

functions performed

by

the

different control commands.

Input

Printout

Function

pc

O:DDDDDDDD

@ 80000000

Enter P-Mode of

operations; contents

of Q register 0 is

normally displayed.

100/

100/

Select

and display

O:DDDDDDDD

@ 00000100

contents of memory

location X'lOO'.

Control Commands 147

Loading...

Loading...