The nonexistent instruction, the privi leged instruction

violation,

and the unimplemented instruction trap conditions

can

never

occur

during

execution

of

the AN

LZ

instruction.

However,

either

the nonexistent memory address condition

or

the memory protection

violation

trap condition (or both)

can

occur

as a result

of

any memory access

initiated

by the

ANLZ instruction. If

either

of

these trap conditions occurs,

the instruction address stored by an

XPSD

in trap location

X

'

40

'

is

always the virtual address

of

the AN

LZ

instruction.

The

detai

led operation

of

ANALYZE is as follows:

1.

The

contents

of

the location pointed to by the

effective

virtual address

of

the

AN

LZ

instruction is

obtained.

This

effective

word is the instruction to be

analyzed.

From

a memory-protection viewpoint, the instruction

(to be

analyzed)

is

treated

as an operand

of

the

ANLZ

instruction;

that

is, the

analyzed

instruction may be

obtained

from any memory

area

to which the program

has read access.

2. If the operation code portion

of

the

effective

word

specifies an immediate-addressing instruction type, the

condition code

is

set

to

indicate

the addressing type,

and instruction

execution

proceeds to the

next

in-

struction in sequence

after

AN

LZ.

The

original

con-

tents

of

register R are not changed when the

analyzed

instruction

is

of

the immediate-addressing type.

If

the operation code portion

of

the

effective

word

specifies a reference-addressing instruction type, the

condition code

is

set to

indicate

the addressing type

of

the

analyzed

instruction and the

effective

address

of

the

analyzed

instruction

is

computed (using

all

of

Tne

normai address compuTaTion ruies). if

biT

0

of

tne

effective

word is a 1, the contents

of

the memory

lo-

cation specified by bits 15-31

of

the

effective

word

are obtained and then used as a

direct

address.

The

nonallowed operation trap (memory protection

viola-

tion or nonexistent memory address)

can

occur

as a

result

of

the memory access. Indexing is always

per-

formed (with an

index

register in the current register

block)

if

bits

12-14

of

the

analyzed

instruction

are

nonzero. During real extended addressing, the

effec-

tive

virtual address

of

the

analyzed

instruction is

aligned

as an

integer

displacement value and loaded

into register

R,

according to the instruction addressing

type, as

follows:

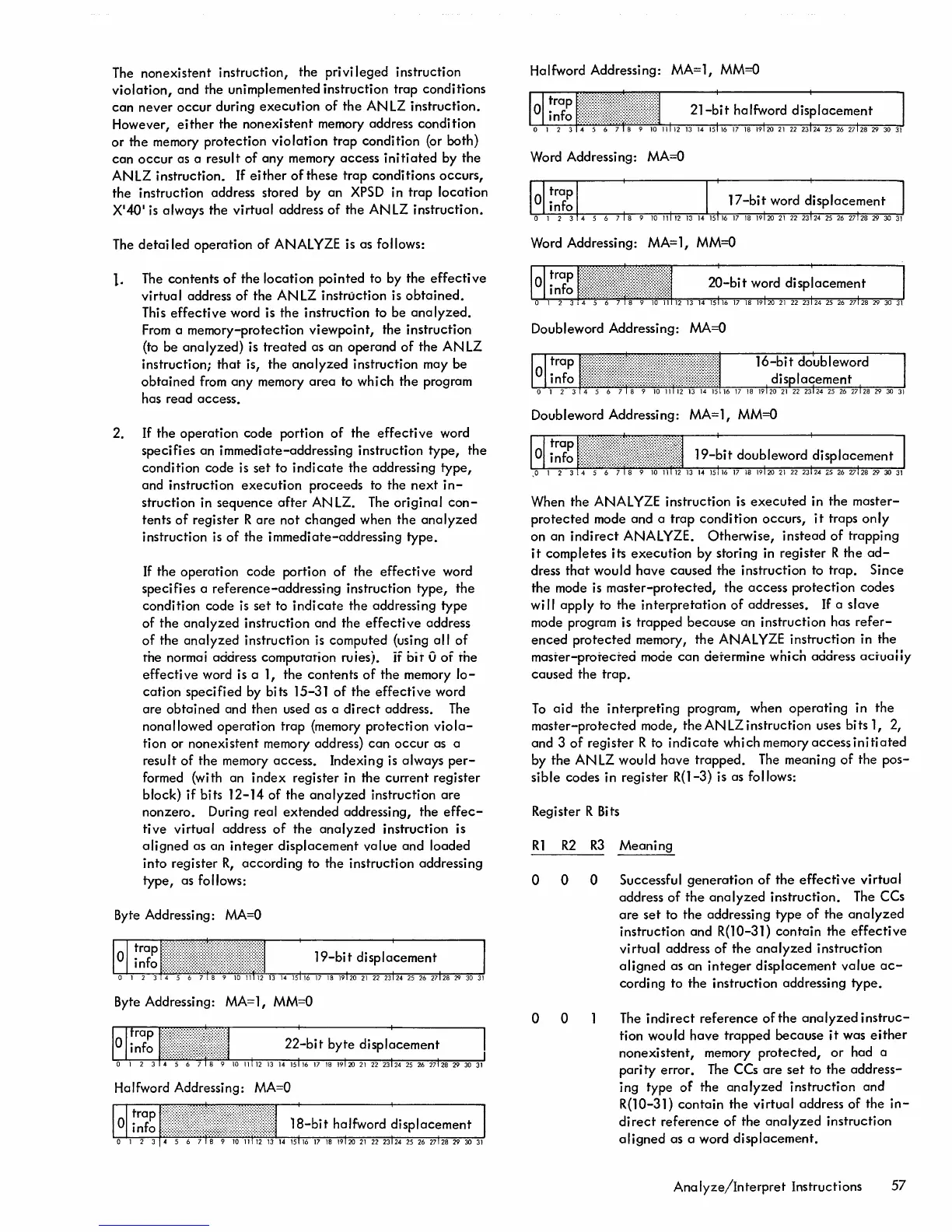

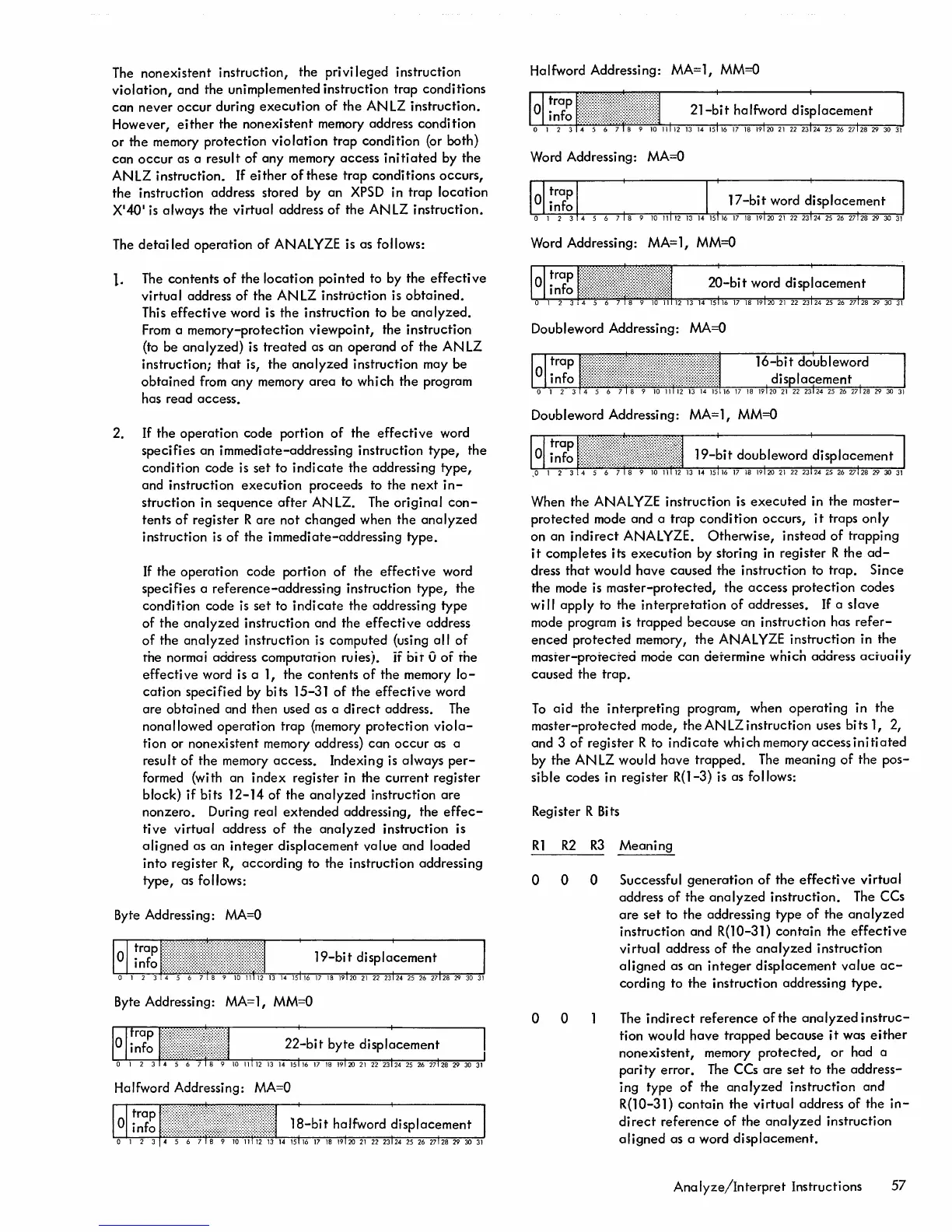

Byte Addressing:

MA=O

Byte Addressing: MA=l,

MM=O

Halfword Addressing:

MA=O

Halfword Addressing:

MA=l,

MM=O

Word Addressing:

MA=O

Word Addressing: MA=l,

MM=O

Doubleword Addressing:

MA=O

Doubleword Addressing:

MA=l,

MM=O

When the ANALYZE instruction is

executed

in the

master-

protected

mode and a trap condition occurs,

it

traps

only

on an

indirect

ANALYZE. Otherwise, instead

of

trapping

it

completes its

execution

by storing in register R the

ad-

dress

that

would have caused the instruction to trap. Since

the mode

is

master-protected,

the access protection codes

wi

II

apply to the

interpretation

of

addresses. If a slave

mode program is trapped because an instruction has

refer-

enced

protected

memory, the ANALYZE instruction in the

master-protected

mode

can

determine which address

aCTuai

iy

caused the trap.

To

aid

the

interpreting

program, when

operating

in the

master-protected

mode, the

AN

LZ

instruction uses bits 1, 2,

and 3

of

register R to

indicate

which memory

access

initiated

by the

AN

LZ

would have trapped.

The

meaning

of

the

pos-

sible codes in register R(1-3) is as follows:

Register R

Bits

R1

R2

R3

Meaning

o 0 0 Successful

generation

of

the

effective

virtual

address

of

the

analyzed

instruction. The CCs

are

set

to the addressing type

of

the

analyzed

instruction and R(10-31) contain the

effective

virtual address

of

the

analyzed

instruction

aligned

as an

integer

displacement

value

ac-

cording to the instruction addressing type.

o 0

The

indirect

reference

of

the

analyzed

instruc-

tion would have trapped because

it

was

either

nonexistent, memory

protected,

or

had a

parity

error.

The

CCs

are

set

to the address-

ing type

of

the

analyzed

instruction and

R(10-31) contain the virtual address

of

the

in-

direct

reference

of

the

analyzed

instruction

aligned

as a word displacement.

Ana

Iyze/Interpret

Instructions 57

Loading...

Loading...