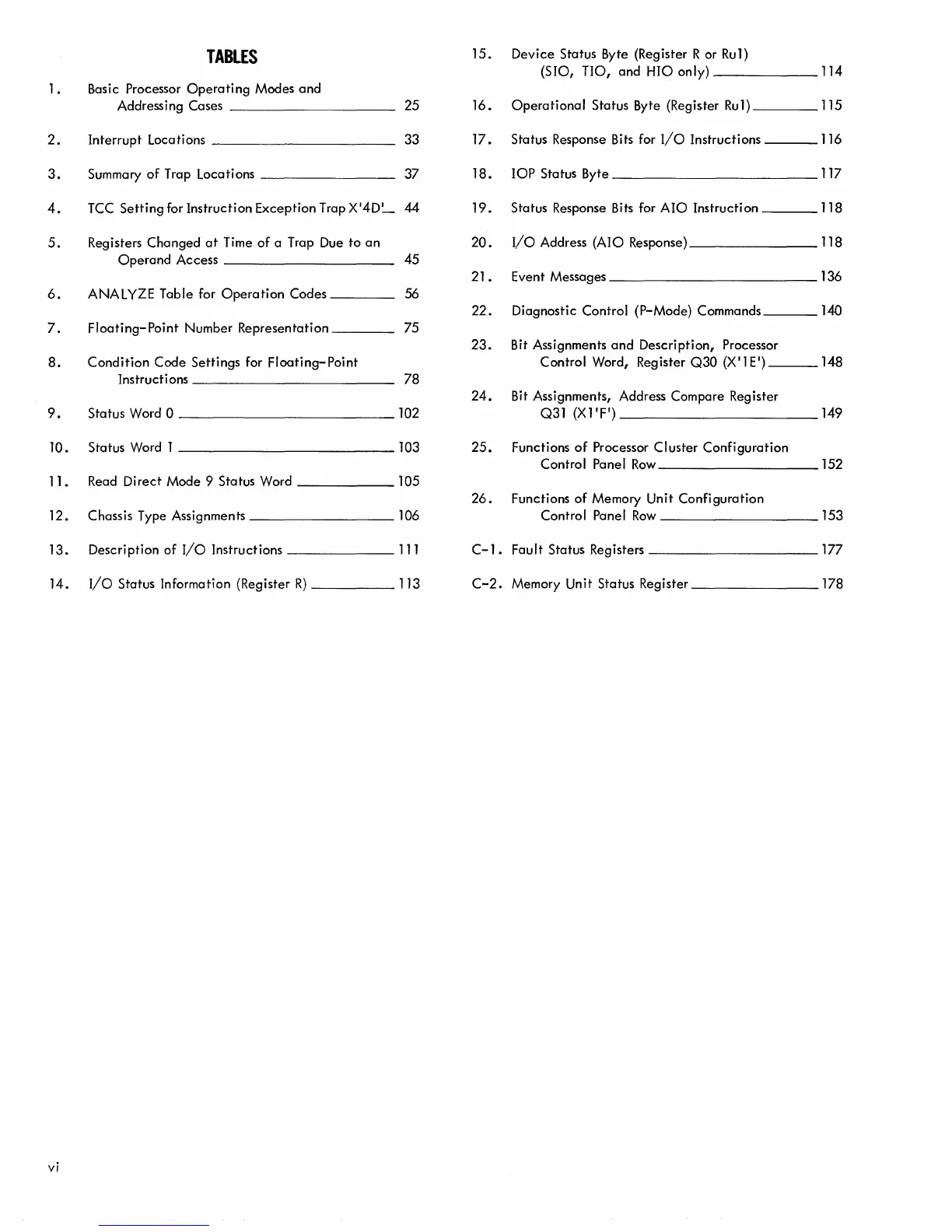

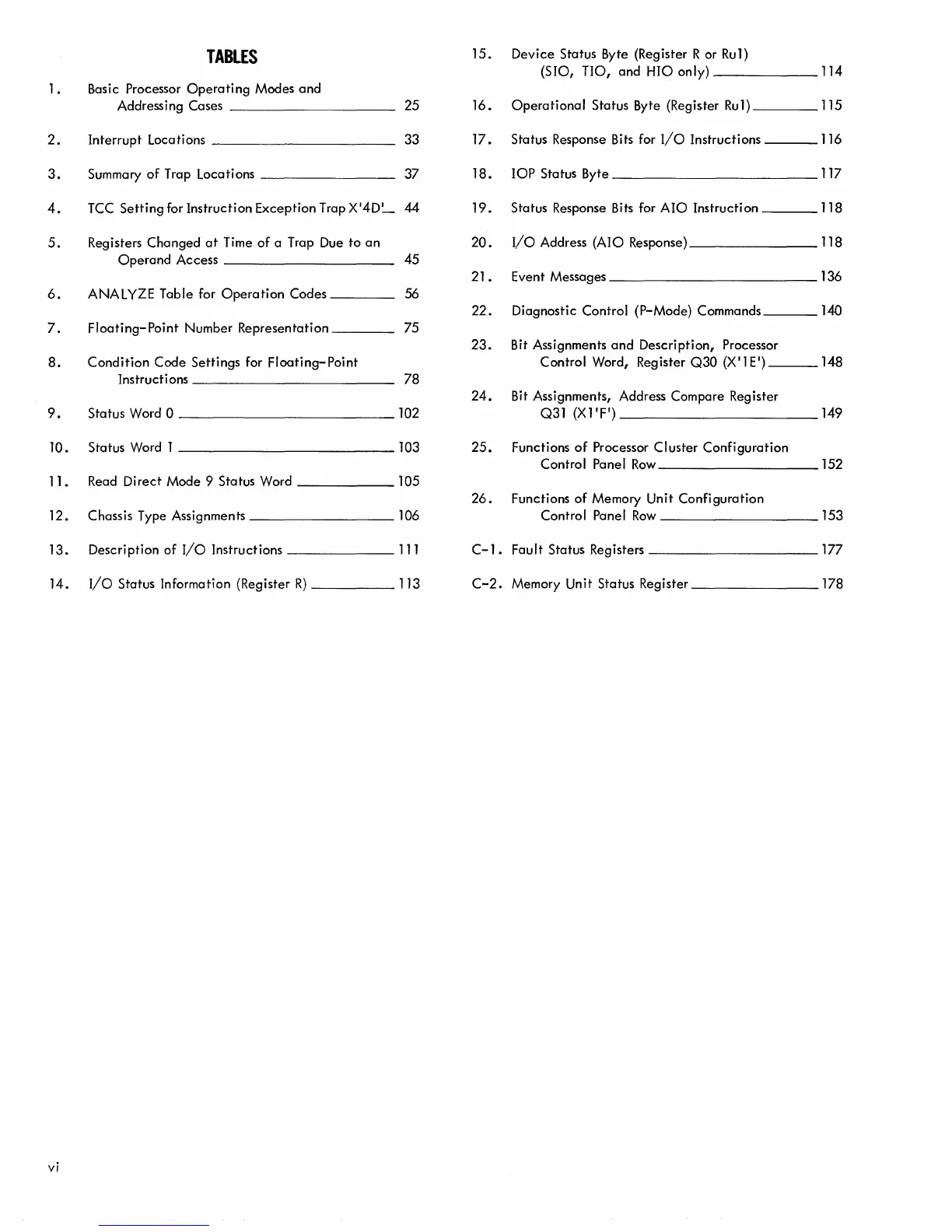

TABLES

15.

Device Status Byte (Register R or

Ru1)

(510,

no,

and

HIO

only) 114

1.

Basic Processor

Operating

Modes

and

Addressing Cases 25

16.

Operational

Status Byte (Register

Ru

1)

115

2.

Interrupt

Locations

33

17.

Status Response Bits for

I/O

Instructions 116

3.

Summary

of

Trap Locations

37

18.

lOP

Status Byte

117

4.

TCC

Setting

for Instruction Exception Trap

X'4D~

44

19.

Status Response Bits for

AIO

Instruction 118

5.

Registers

Changed

at

Time

of

a Trap Due to

an

20.

I/O

Address (AIO Response) 118

Operand

Access

45

21.

Event Messages 136

6.

ANALYZE Table for

Operation

Codes 56

22.

Diagnostic Control (P-Mode) Commands 140

7.

Floating-Point

Number Representation

75

23.

Bit Assignments

and

Description, Processor

8.

Condition

Code Settings for

Floating-Point

Control Word, Register

Q30

(X'l

E') 148

Instructions

78

24.

Bit

Assignments, Address Compare Register

9.

Status Word 0 102

Q31

(X1'F')

149

10.

Status Word 1

103

25.

Functions

of

Processor

Cluster

Configuration

Control

Panel

Row

152

11.

Read Direct Mode 9 Status Word

105

26.

Functions

of

Memory Unit Configuration

12.

Chassis Type Assignments

106

Control Panel

Row

153

13.

Description of

I/o

Instructions

111

C-1.

Fault Status Registers

177

14.

I/o

Status Information (Register

R)

113

C-2.

Memory Unit Status Register

178

vi

Loading...

Loading...