PSS

PUSH

STATUS

(Doubleword

index

alignment, privi leged)

H OD

PUSH

STATUS

loads new Program Status Words from an

ef-

fective

doubleword location and stores

the

current

environ-

ment (current Program Status Words and contents

of

all

16 general registers) into a memory

stack,

as defined by the

Status Stack Pointer Doubleword.

Note

that

the

reference

address points to the memory location

of

the new

PSWs.

The

PSS

instruction is used for three types

of

operations:

as a normal instruction in an ongoing program; as an

inter-

rupt instruction; and as a trap instruction.

The

effective

address

of

a

PSS

instruction

is

generated

in

one

of

the

following ways:

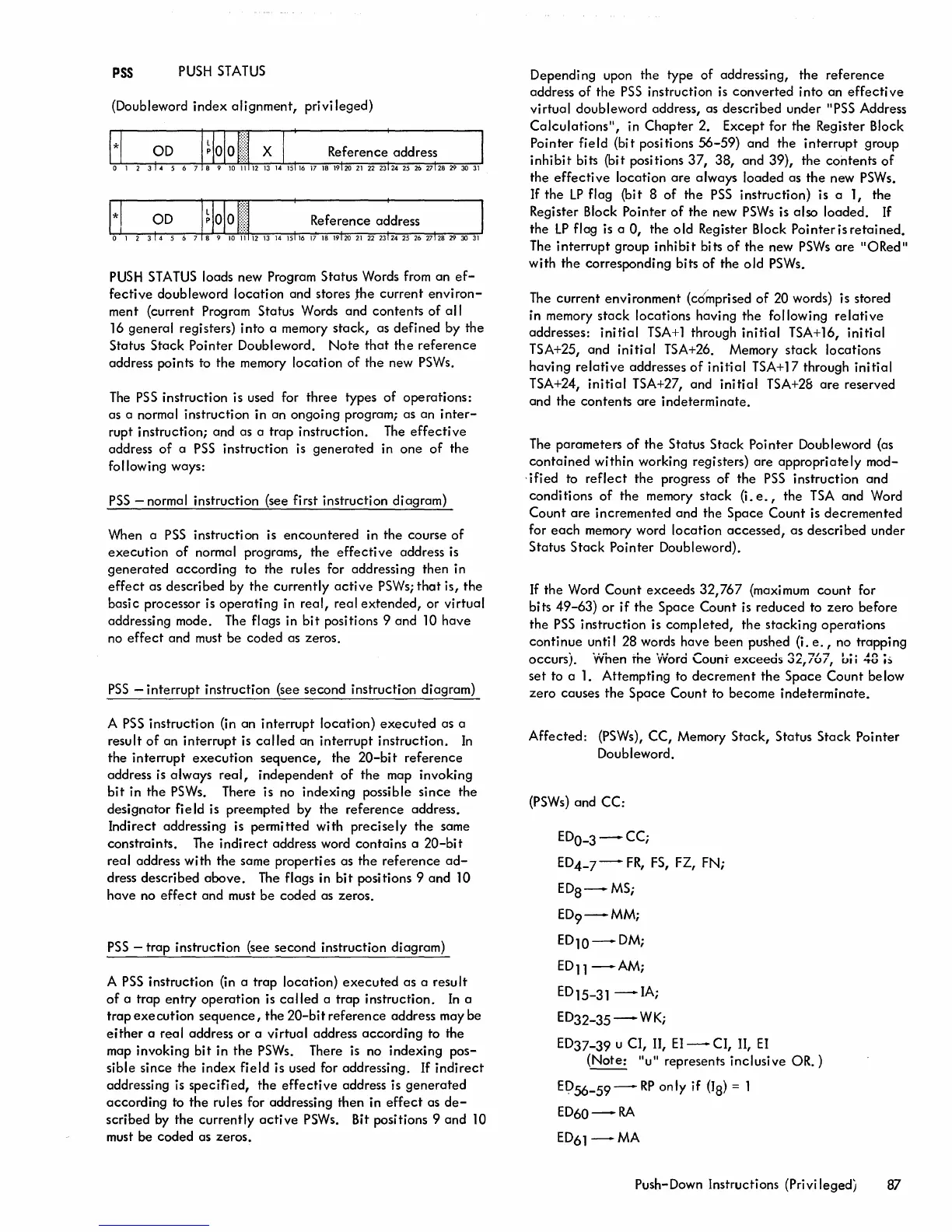

PSS

- normal instruction (see first instruction diagram)

When a

PSS

instruction

is

encountered in the course

of

execution

of

normal programs, the

effective

address

is

generated

according to the rules for addressing then in

effect

as described by the currently

active

PSWSi

that

is, the

basic processor is

operating

in

real,

real

extended,

or virtual

addressing mode. The flags in

bit

positions 9 and

10

have

no

effect

and must be coded as zeros.

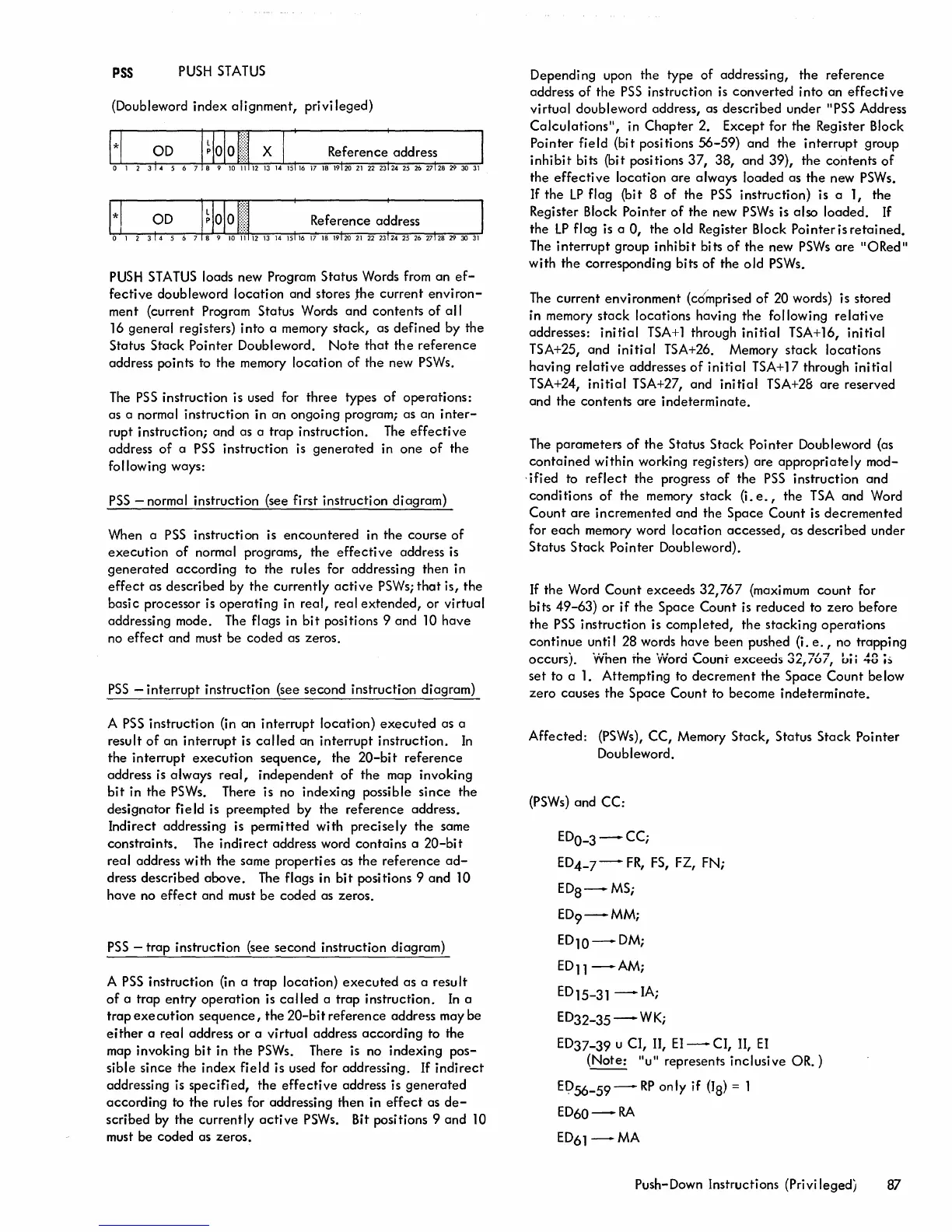

PSS

- interrupt instruction (see second instruction diagram)

A

PSS

instruction (in an interrupt location)

executed

as a

result

of

an interrupt is

called

an interrupt instruction.

In

the interrupt

execution

sequence,

the

20-bit

reference

address

is

always

real,

independent

of

the map invoking

bit

in the

PSWs.

There is no indexing possible since the

designator field is preempted by the reference address.

Indirect addressing is permitted with

precisely

the same

constraints.

The

indirect

address word contains a

20-bit

real address with the same properties as the reference

ad-

dress described

above.

The flags in

bit

positions 9 and 10

have no

effect

and must be coded as zeros.

PSS

- trap instruction (see second instruction diagram)

A

PSS

instruction

(in

a trap location)

executed

as a result

of

a trap entry operation is

called

a trap instruction.

In

a

trap

execution

sequence,

the

20-bit

reference address may be

either

a real address

or

a virtual address according to the

map invoking

bit

in the

PSWs.

There

is

no indexing

pos-

sible since the

index

field is used for addressing. If

indirect

addressing is specified, the

effective

address is

generated

according to

the

rules for addressing then in

effect

as

de-

scribed

by

the currently

active

PSWs.

Bit positions 9 and

10

must be coded as zeros.

Depending upon the type of addressing, the

reference

address

of

the

PSS

instruction

is

converted into an

effective

virtual doubleword address, as described under

IIpSS

Address

Calculations",

in

Chapter

2. Except for the Register Block

Pointer field (bit positions

56-59)

and the

interrupt

group

inhibit

bits (bit positions

37,

38,

and 39), the contents

of

the

effective

location

are

always loaded as

the

new

PSWs.

If

the

LP

flag (bit 8

of

the

PSS

instruction) is a 1, the

Register Block Pointer

of

the new

PSWs

is also loaded. If

the

LP

flag

is

a

0,

the old Register Block

Pointerisretained.

The interrupt group

inhibit

bits

of

the new

PSWs

are

"ORed

ll

with the corresponding bits

of

the old

PSWs.

The

current environment (comprised

of

20 words) is stored

in memory

stack

locations having the following

relative

addresses:

initial

TSA+1

through

initial

TSA+16,

initial

TSA+25, and

initial

TSA+26. Memory

stack

locations

having

relative

addresses

of

init'ial TSA+17 through

initial

TSA+24,

initial

TSA+27, and

initial

TSA+28

are

reserved

and the contents

are

indeterminate.

The parameters

of

the Status Stack Pointer Doubleword (as

contained

within working registers)

are

appropriately

mod-

, ifi ed to

reflect

the progress

of

the

PSS

instruction and

conditions

of

the memory stack (i.

e.,

the

TSA

and Word

Count

are

incremented and the Space Count is decremented

for

each

memory word location accessed, as described under

Status

Stack

Pointer Doubleword).

If the Word

Count

exceeds

32,767

(maximum count for

bits

49-63)

or

if

the Space Count

is

reduced to zero before

the

PSS

instruction is completed, the stacking operations

continue until 28 words have been pushed

(i.

e.,

no trapping

.......

1

'I".

,,..

~

I

I"\n~'~

._.

An-_

occurs).

VVnen

me

vvora

~ounr

exceeas

';>£,

lUI,

or

I

'TO

I~

set

to a

1.

Attempting to

decrement

the Space Count below

zero

causes

the

Space Count to become indeterminate.

Affected: (PSWs),

CC, Memory

Stack,

Status Stack Pointer

Doubleword.

(PSWs)

and CC:

EDO_3-CCi

ED4-7-

FR,

FS,

FZ, FN;

ED8-MS;

ED9-MMi

ED10-DM;

EDll-AMi

ED15-31

-IAi

ED32-35-WKi

ED37-39 u CI, II,

EI

- CI, II,

EI

(Note:

IIU"

represents inclusive OR. )

EQ56-59-

RP

only if

(IS)

= 1

ED60-RA

ED61-MA

Push-Down Instructions (Privi leged) 87

Loading...

Loading...