KC705 Evaluation Board 33

UG810 (v1.8) March 20, 2018 www.xilinx.com

Chapter 1: KC705 Evaluation Board Features

For more information about the Silicon Labs Si5324 see [Ref 7].

GTX Transceivers

[Figure 1-2, callout 12]

The KC705 board provides access to 16 GTX transceivers:

• Eight of the GTX transceivers are wired to the PCI Express® x8 endpoint edge

connector (P1) fingers

• Four of the GTX transceivers are wired to the FMC HPC connector (J22)

• One GTX is wired to the FMC LPC connector (J2)

• One GTX is wired to SMA connectors (RX: J17, J18 TX: J19, J20)

• One GTX is wired to the SFP/SFP+ Module connector (P5)

• One GTX is used for the SGMII connection to the Ethernet PHY (U37)

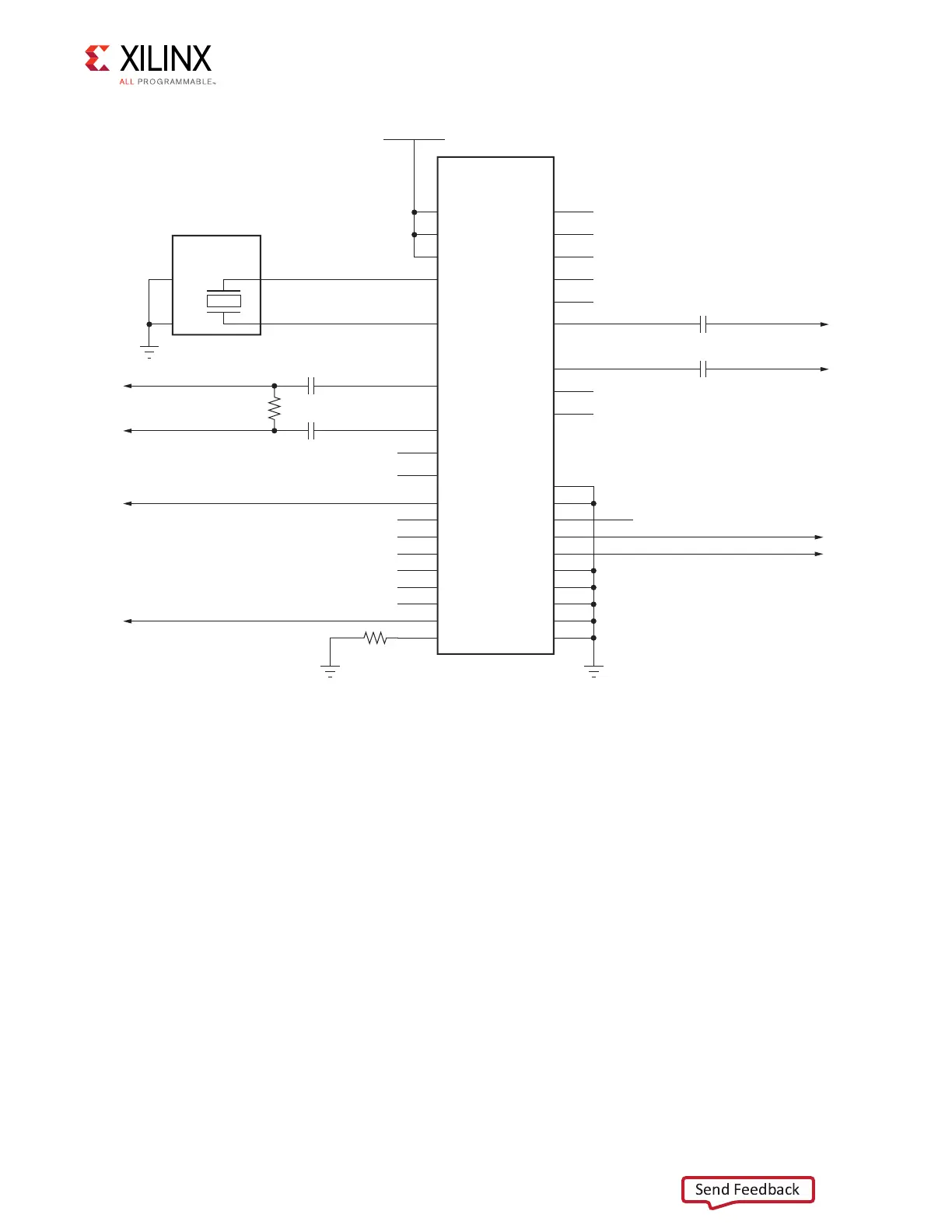

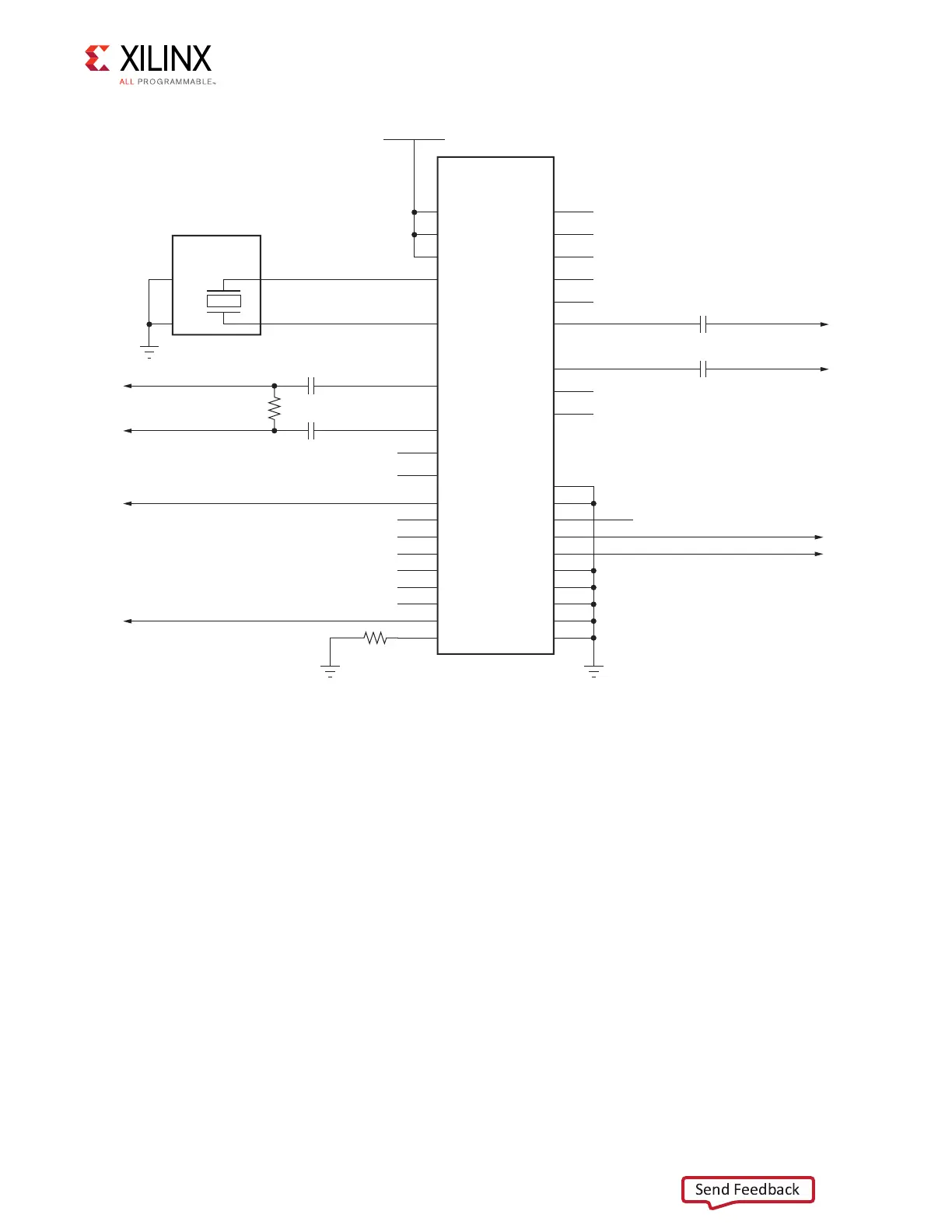

X-Ref Target - Fig ure 1-14

Figure 1-14: Jitter Attenuated Clock

UG810_c1_14_031214

R424

4.7KΩ 5%

SI5326_VCC

Si5324C-C-GM

Clock Multiplier/

Jitter Attenuator

VDDA

GND

XB

XA

NC5

32

6

5

29

28

U70

CKOUT1_N

7

8

CKOUT1_P

C473

0.1μF 25V

X5R

C474

0.1μF 25V

X5R

SI5326_XTAL_XA

GND2

GND1

XB

XA

X5

114.285 MHz

20 ppm

SI5326_OUT_C_N

SI5326_OUT_C_P

SI5326_OUT_N

SI5326_OUT_P

SI5326_XTAL_XB

GND

NC4

2

1

3

4

C475

0.1μF 25V

X5R

C476

0.1μF 25V

X5R

REC_CLOCK_P

REC_CLOCK_N

REC_CLOCK_C_P

REC_CLOCK_C_N

16

17

R337

100Ω

CKIN1_P

CKIN1_N

NC

NC

12

13

CKIN2_P

CKIN2_N

10

5

VDDA

VDDA

2

NC3

2

NC2

2

NC1

NC

NC

NC

NC

NC

35

34

NC

NC

CKOUT2_N

CKOUT2_P

SI5326_INT_ALM 3

NC 4

NC 11

NC 15

NC 18

NC 19

NC 20

SI5326_RST 1

21

31

GND2

9

GND1

31

A2_SS

31

A1

24

A0

22

SI5326_SCL

SCL

23

SI5326_SDA

SDA_SDO

27

NC

SDI

36

CMODE

GND

INC

DEC

LOL

RATE1

RATE0

C2B

INT_C1B

CS_CA

RST_B

37

GNDPAD

Loading...

Loading...