KC705 Evaluation Board 42

UG810 (v1.8) March 20, 2018 www.xilinx.com

Chapter 1: KC705 Evaluation Board Features

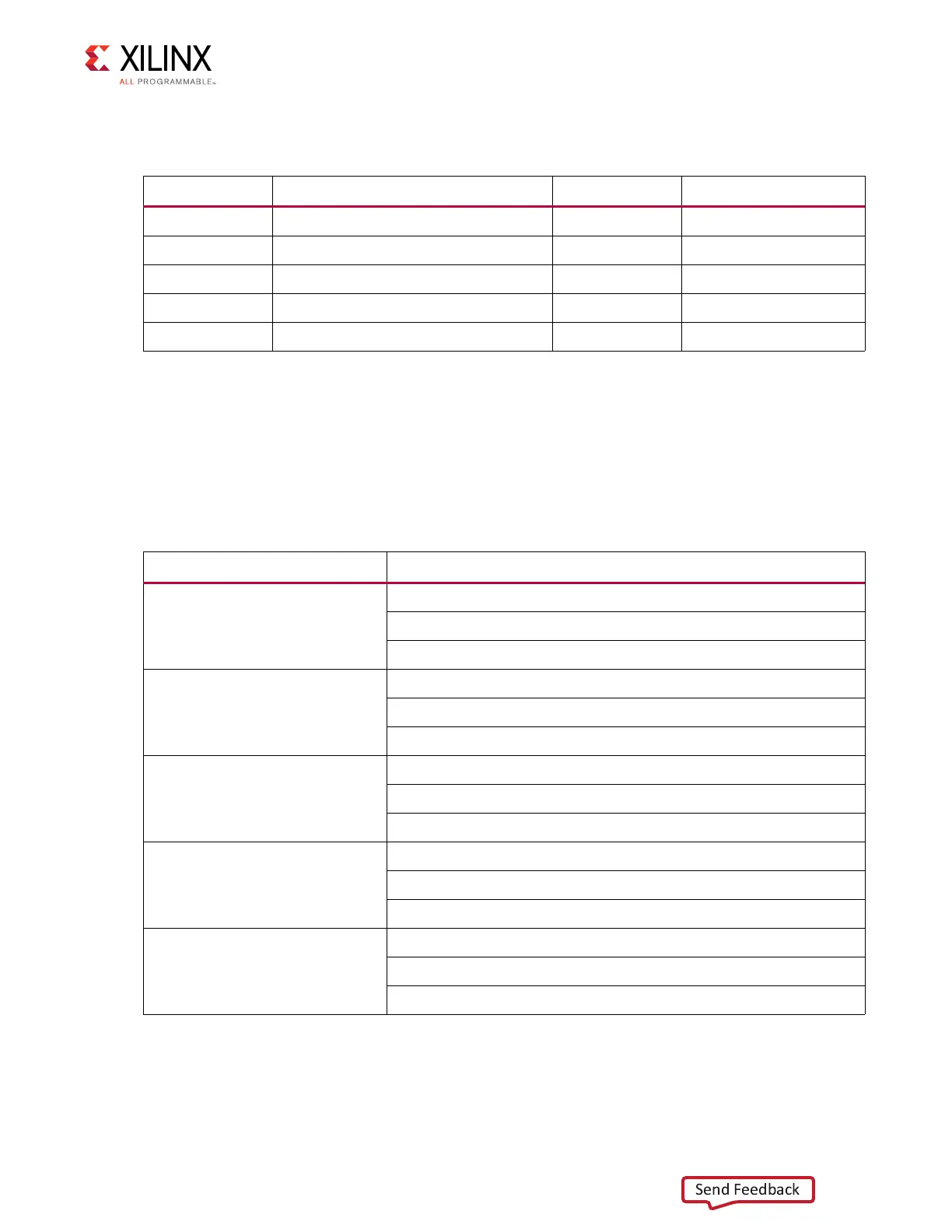

Table 1-14 lists the SFP+ module RX and TX connections to the FPGA.

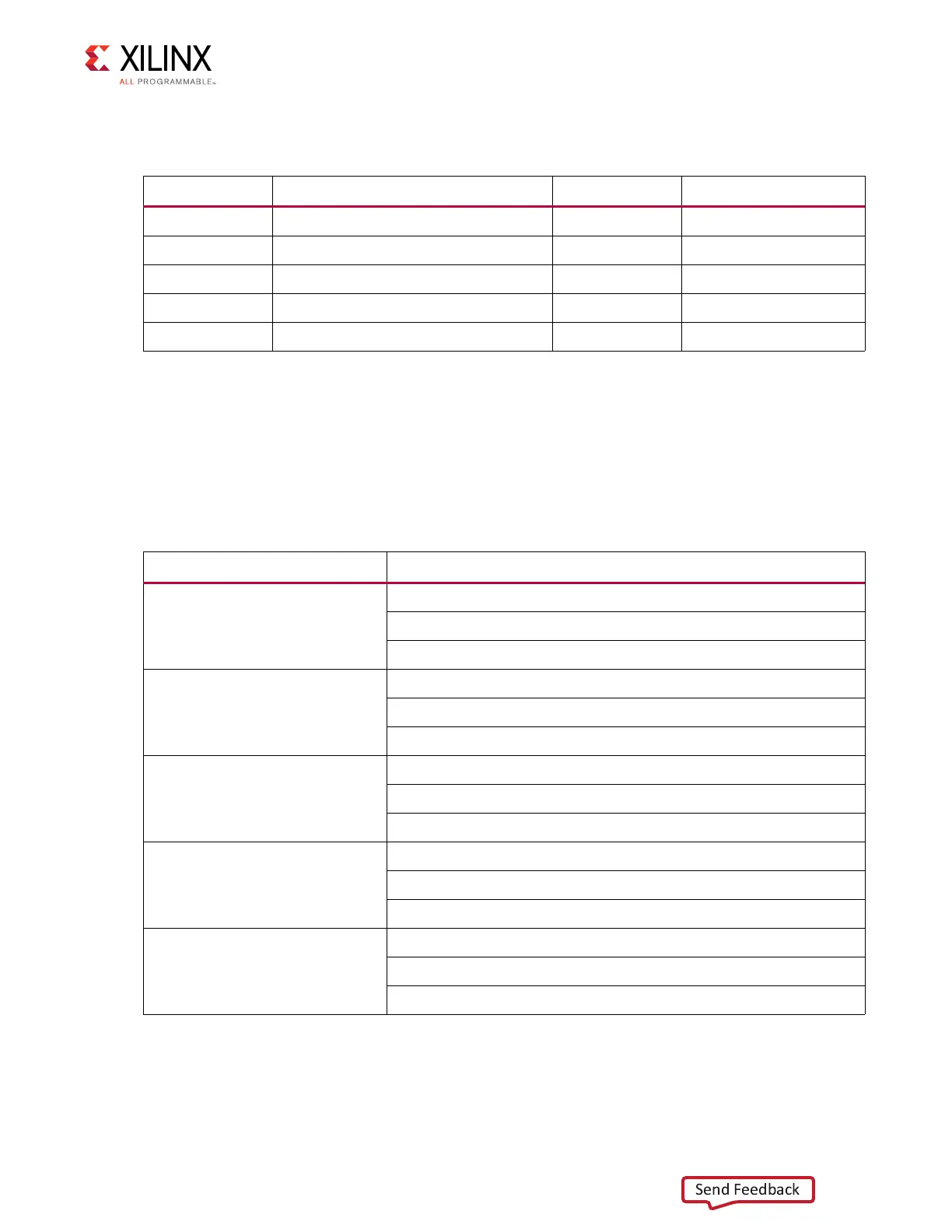

Table 1-15 lists the SFP+ module control and status connections to the FPGA.

Table 1-14: FPGA U1 to SFP+ Module Connections

FPGA Pin (U1) Schematic Net Name SFP+ Pin (P5) SFP+ Pin Name (P5)

G3 SFP_RX_N 12 RD_N

(1)

G4 SFP_RX_P 13 RD_P

(1)

H1 SFP_TX_N 19 TX_N

(2)

H2 SFP_TX_P 18 TX_P

(2)

Y20 SFP_TX_DISABLE_TRANS

(3)

3TX_DISABLE

Notes:

1. On KC705 boards prior to Rev 1.1, SFP+ connector P5 pin 18 RD_P is connected to net SFP_RX_N, and pin 19 RD_N

is connected to net SFP_RX_P.

2. On KC705 boards prior to Rev 1.1, SFP+ connector P5 pin 18 TD_P is connected to net SFP_TX_N, and pin 19 TD_N

is connected to net SFP_TX_P.

3. SFP_TX_DISABLE_TRANS I/O standard = LVCMOS25.

Table 1-15: SFP+ Module Control and Status

SFP Control/Status Signal Board Connection

SFP_TX_FAULT Test Point J10

High = Fault

Low = Normal Operation

SFP_TX_DISABLE Jumper J4

Off = FP Disabled

On = SFP Enabled

SFP_MOD_DETECT Test Point J9

High = Module Not Present

Low = Module Present

SFP_RS0 Jumper J27

Jumper Pins 1-2 = Full RX Bandwidth

Jumper Pins 2-3 = Reduced RX Bandwidth

SFP_RS1 Jumper J28

Jumper Pins 1-2 = Full TX Bandwidth

Jumper Pins 2-3 = Reduced TX Bandwidth

Loading...

Loading...