KC705 Evaluation Board 45

UG810 (v1.8) March 20, 2018 www.xilinx.com

Chapter 1: KC705 Evaluation Board Features

Details about the tri-mode Ethernet MAC core are provided in LogiCORE IP Tri-Mode

Ethernet MAC User Guide (PG051) [Ref 14].

For more information about the Marvell 88E1111, see [Ref 15].

For more information about the ICS 844021-01, see [Ref 16].

USB-to-UART Bridge

[Figure 1-2, callout 17]

The KC705 board contains a Silicon Labs CP2103GM USB-to-UART bridge device (U12)

which allows a connection to a host computer with a USB port. The USB cable is supplied in

the Evaluation Kit (standard-A plug to host computer, mini-B plug to KC705 board

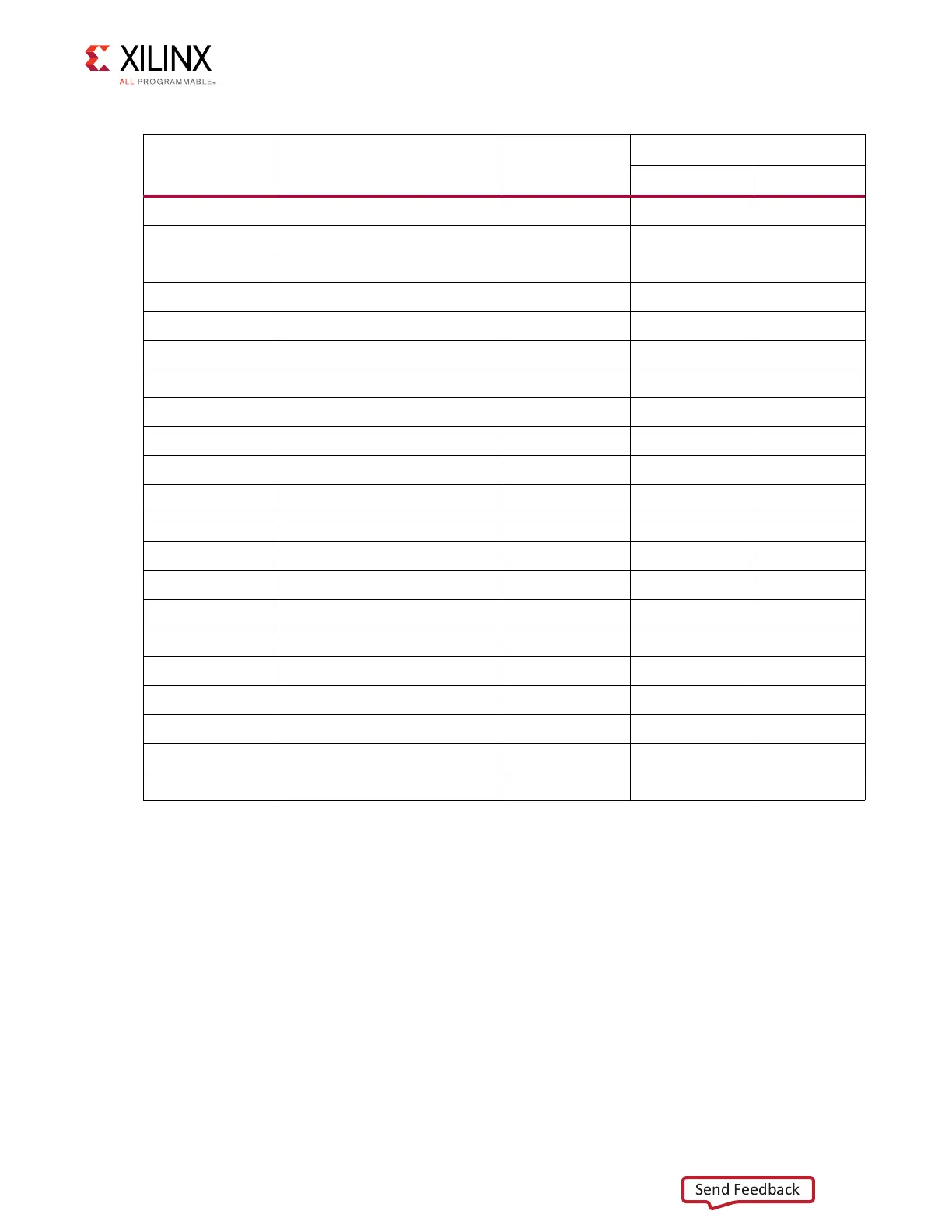

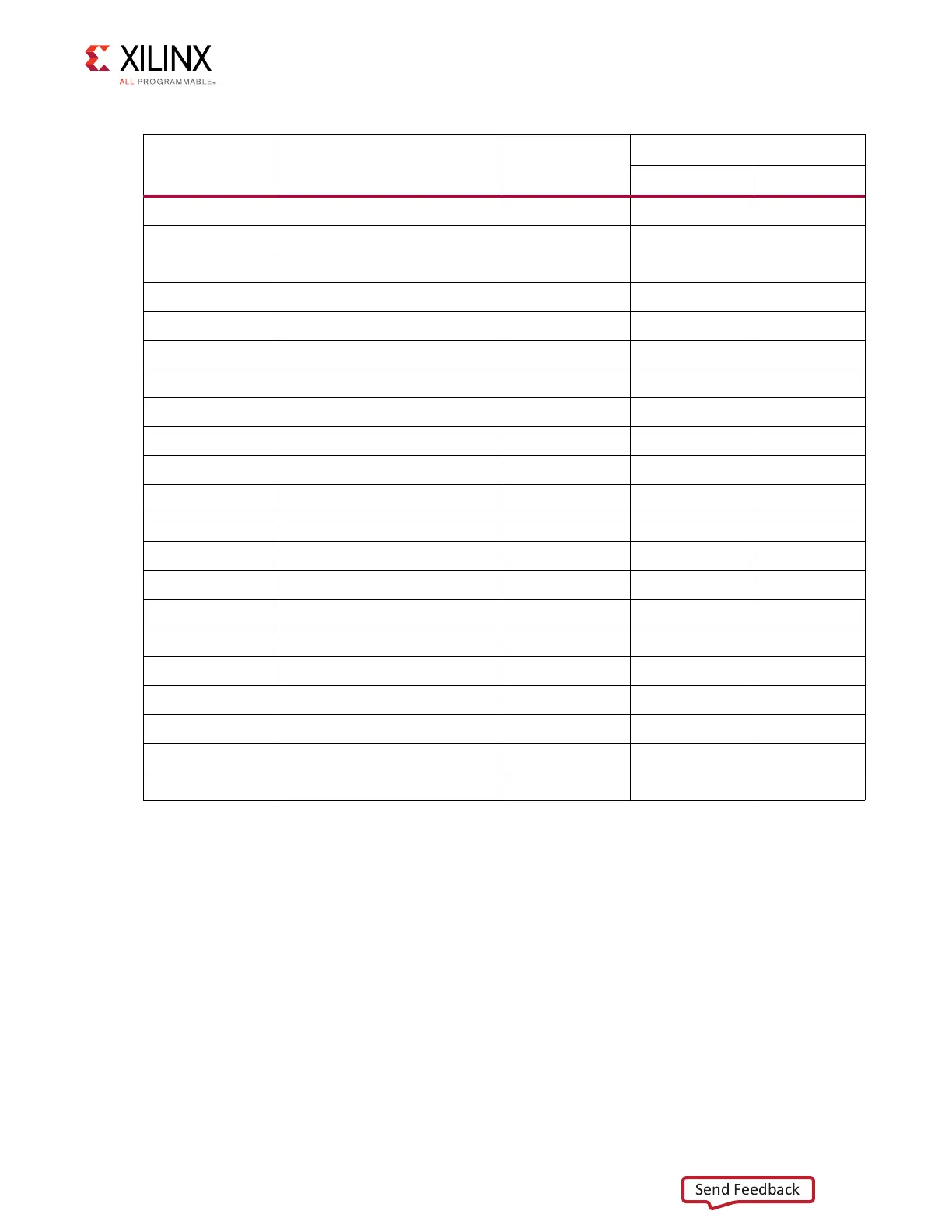

U28 PHY_RXD3 LVCMOS25 B3 RXD3

R19 PHY_RXD4 LVCMOS25 C4 RXD4

T27 PHY_RXD5 LVCMOS25 A1 RXD5

T26 PHY_RXD6 LVCMOS25 A2 RXD6

T28 PHY_RXD7 LVCMOS25 C5 RXD7

K30 PHY_TXC_GTXCLK LVCMOS25 E2 GTXCLK

M28 PHY_TXCLK LVCMOS25 D1 TXCLK

N29 PHY_TXER LVCMOS25 F2 TXER

M27 PHY_TXCTL_TXEN LVCMOS25 E1 TXEN

N27 PHY_TXD0 LVCMOS25 F1 TXD0

N25 PHY_TXD1 LVCMOS25 G2 TXD1

M29 PHY_TXD2 LVCMOS25 G3 TXD2

L28 PHY_TXD3 LVCMOS25 H2 TXD3

J26 PHY_TXD4 LVCMOS25 H1 TXD4

K26 PHY_TXD5 LVCMOS25 H3 TXD5

L30 PHY_TXD6 LVCMOS25 J1 TXD6

J28 PHY_TXD7 LVCMOS25 J2 TXD7

J4 SGMII_TX_P LVCMOS25 A3 SIN_P

J3 SGMII_TX_N LVCMOS25 A4 SIN_N

H6 SGMII_RX_P LVCMOS25 A7 SOUT_P

H5 SGMII_RX_N LVCMOS25 A8 SOUT_N

Table 1-18: Ethernet PHY Connections (Cont’d)

U1 FPGA Pin Schematic Net Name I/O Standard

M88E1111 (U37)

Pin Number Pin Name

Loading...

Loading...