KC705 Evaluation Board 78

UG810 (v1.8) March 20, 2018 www.xilinx.com

Chapter 1: KC705 Evaluation Board Features

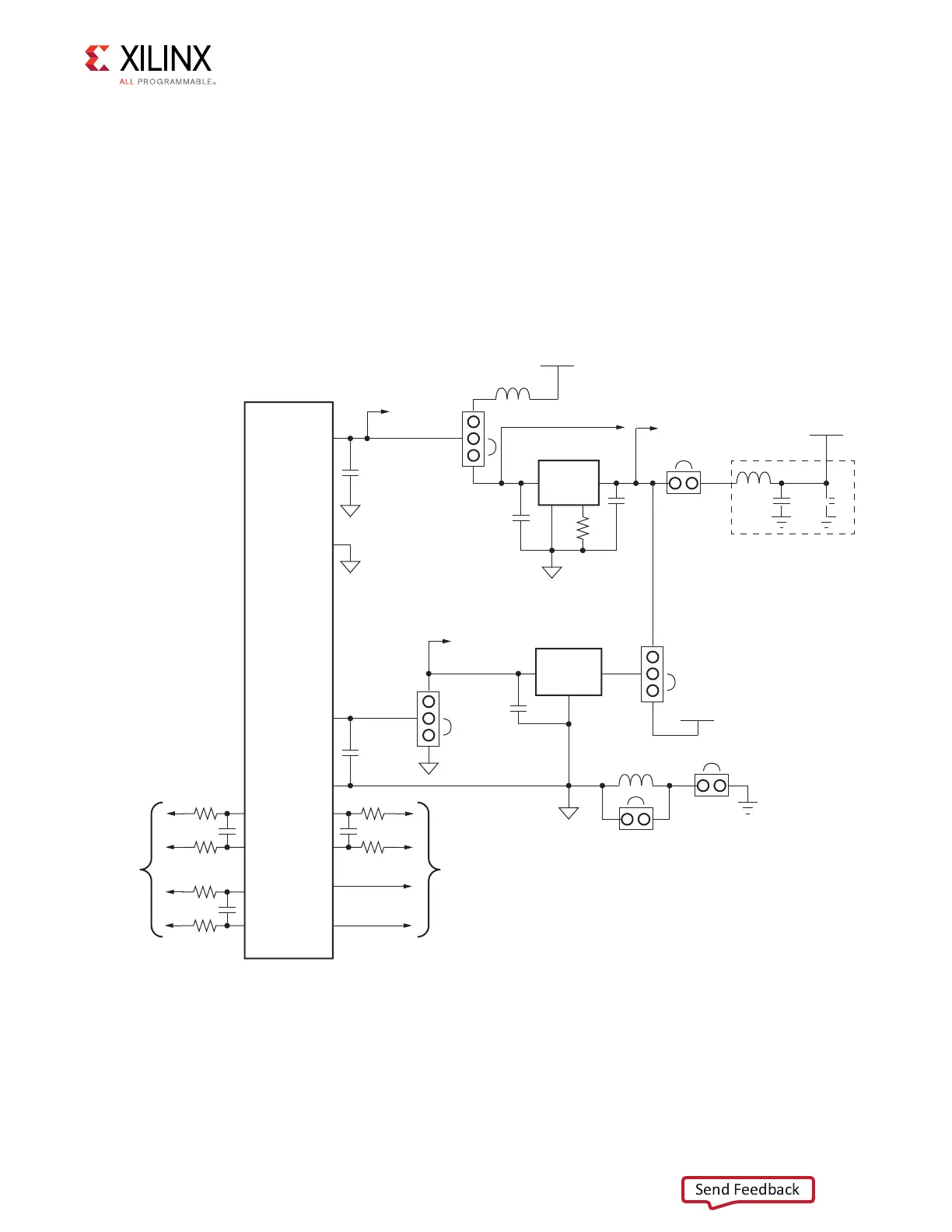

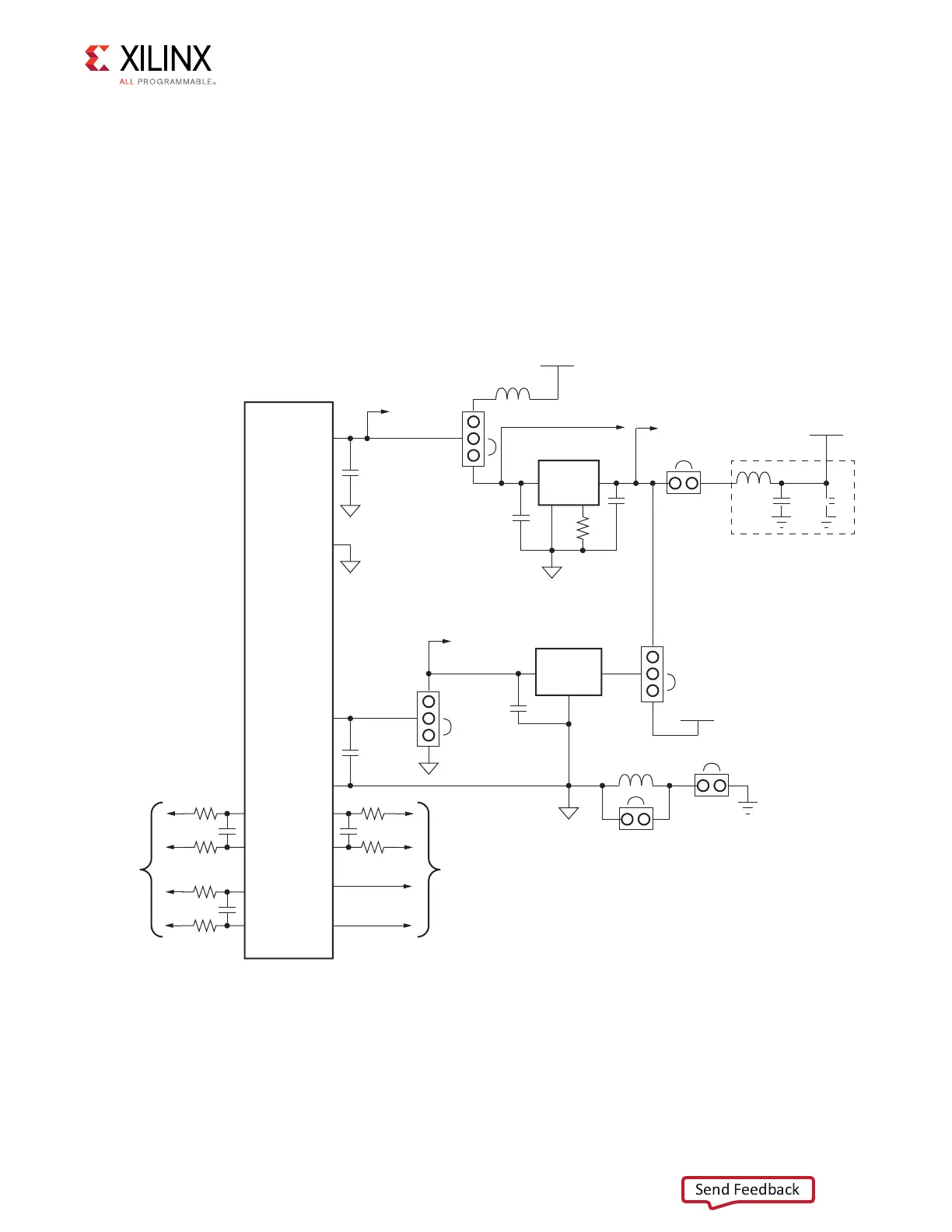

XADC Header

[Figure 1-2, callout 33]

7 series FPGAs provide an analog-to-digital converter (XADC) block. The XADC block

includes a dual 12-bit, 1 MSPS analog-to-digital converter (ADC) and on-chip sensors.

See 7 Series FPGAs XADC Dual 12-Bit 1MSPS Analog-to-Digital Converter User Guide

(UG480) [Ref 25] for details on the capabilities of the analog front end. Figure 1-37 shows

the KC705 board XADC support features.

The KC705 board supports both the internal FPGA sensor measurements and the external

measurement capabilities of the XADC. Internal measurements of the die temperature,

VCCINT, VCCAUX, and VCCBRAM are available. The KC705 board VCCINT and VCCBRAM are

provided by a common 1.0 V supply.

X-Ref Target - Fig ure 1-37

Figure 1-37: Header XADC_VREF Voltage Source Options

FPGA

U1

VAUX0N

VAUX0P

VAUX8N

VAUX8P

V

REF (1.25V)

V

REFN

VCCADC

GNDADC

V

N

V

P

DXP

DXN

UG810_c1_37_031214

100Ω

1 nF

100Ω

100Ω

1 nF

100Ω

To

Header

J46

Dual Use IO

(Analog/Digital)

100Ω

1 nF

100Ω

To

Header

J46

100 nF

XADC_AGND

REF3012

U42

Out In

Gnd

J47

XADC_AGND

Internal

Reference

To Header J46

10 μF

Ferrite Bead

100 nF

1 nF

Ferrite Bead

J43

J42

Star Grid

Connection

J69

XADC_VCC

XADC_AGND

GND

V

REFP

V

REFP

ADP123

U39

Out

In

Gnd

XADC_AGND

1 μF

XADC_VCC Header J46

100 nF

XADC_AGND

To J69.3

XADC_VCC

J48

Ferrite Bead

VCCAUX

VCC5V0

10 μF

AV_5V To Header J46

1.8V 150 mV max

J68

Filter 5V Supply

Locate Components on Board

Close to

Package Pins

Close to

Package Pins

Loading...

Loading...