KC705 Evaluation Board 64

UG810 (v1.8) March 20, 2018 www.xilinx.com

Chapter 1: KC705 Evaluation Board Features

°

34 LA pairs (LA00-LA33)

°

24 HA pairs (HA00-HA23)

•4 GTX transceivers

•2 GTX clocks

• 2 differential clocks

• 159 ground and 15 power connections

The HPC signals are distributed across GTX Quads 116, 117, and 118. Each of these Quads

have their VCCO voltage connected to VADJ.

Note:

The KC705 board VADJ voltage for the J22 and J2 connectors is determined by the FMC VADJ

power sequencing logic described in Power Management, page 71.

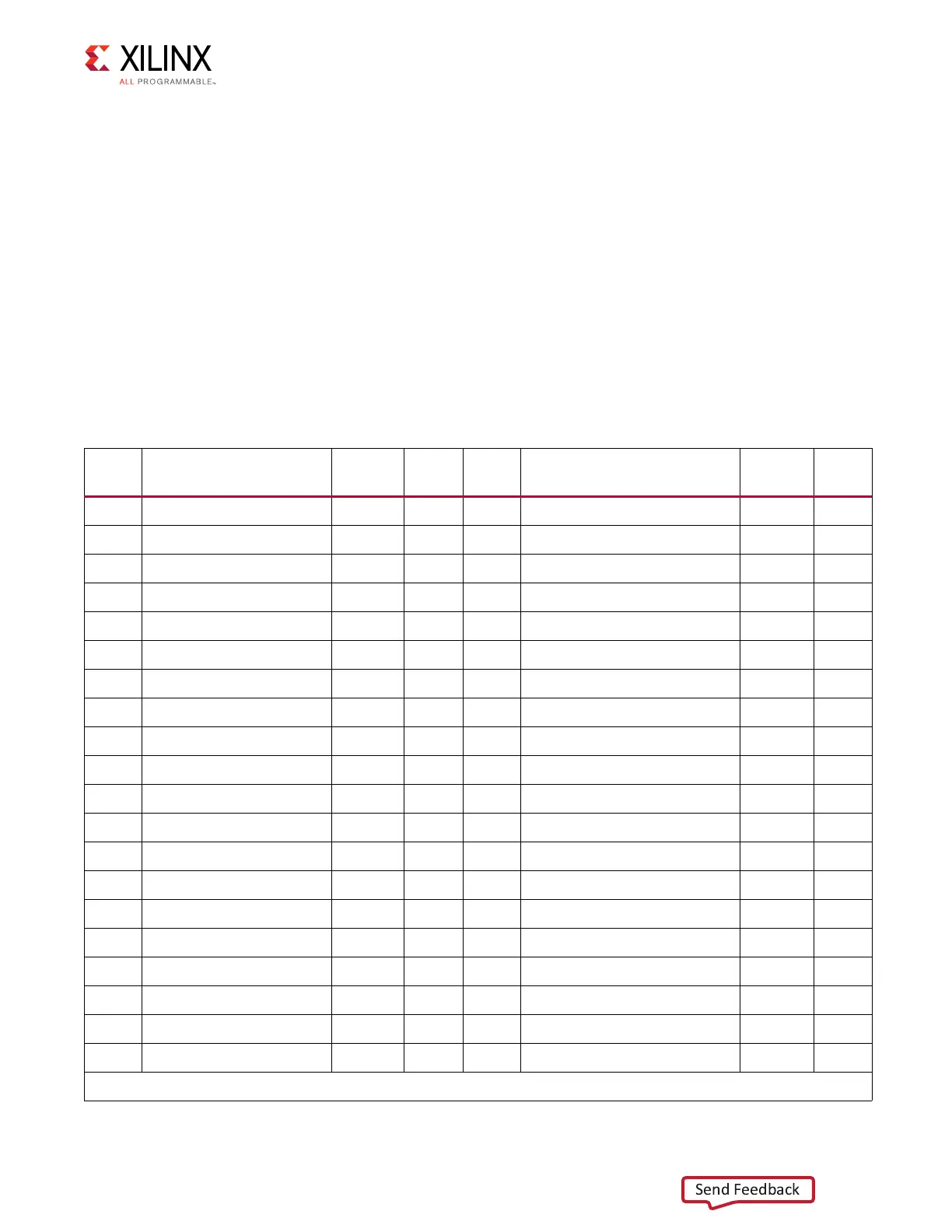

Table 1-28: HPC Connections, J22 to FPGA U1

J22 Pin Schematic Net Name

I/O

Standard

FPGA

U1 Pin

J22 Pin Schematic Net Name

I/O

Standard

FPGA

U1 Pin

A2 FMC_HPC_DP1_M2C_P D6 B1 NC

A3 FMC_HPC_DP1_M2C_N D5 B4 NC

A6 FMC_HPC_DP2_M2C_P B6 B5 NC

A7 FMC_HPC_DP2_M2C_N B5 B8 NC

A10 FMC_HPC_DP3_M2C_P A8 B9 NC

A11 FMC_HPC_DP3_M2C_N A7 B12 NC

A14 NC B13 NC

A15 NC B16 NC

A18 NC B17 NC

A19 NC B20 FMC_HPC_GBTCLK1_M2C_P LVDS E8

A22 FMC_HPC_DP1_C2M_P C4 B21 FMC_HPC_GBTCLK1_M2C_N LVDS E7

A23 FMC_HPC_DP1_C2M_N C3 B24 NC

A26 FMC_HPC_DP2_C2M_P B2 B25 NC

A27 FMC_HPC_DP2_C2M_N B1 B28 NC

A30 FMC_HPC_DP3_C2M_P A4 B29 NC

A31 FMC_HPC_DP3_C2M_N A3 B32 NC

A34 NC B33 NC

A35 NC B36 NC

A38 NC B37 NC

A39 NC B40 NC

Loading...

Loading...