January 2007 293

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

Schematic Checklist Summary

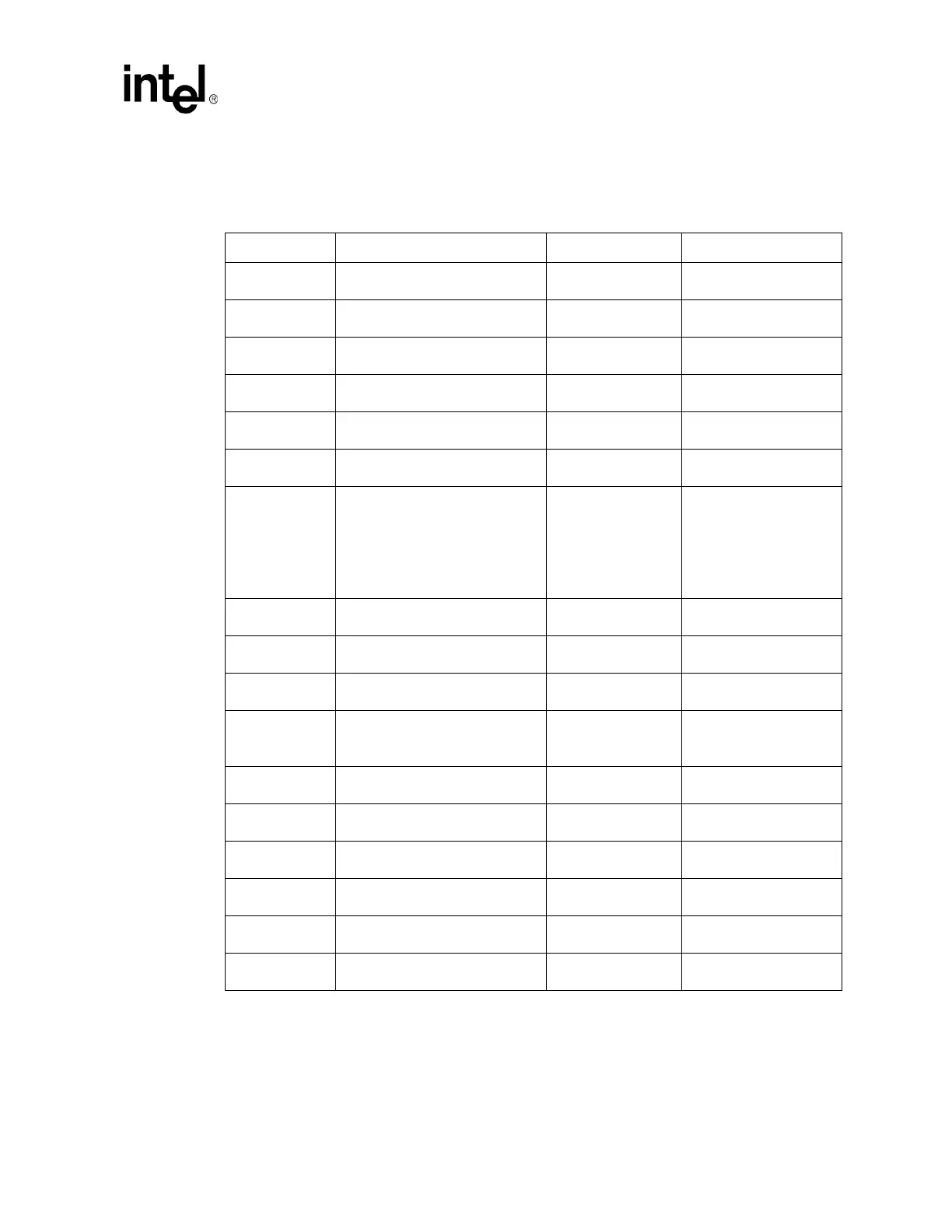

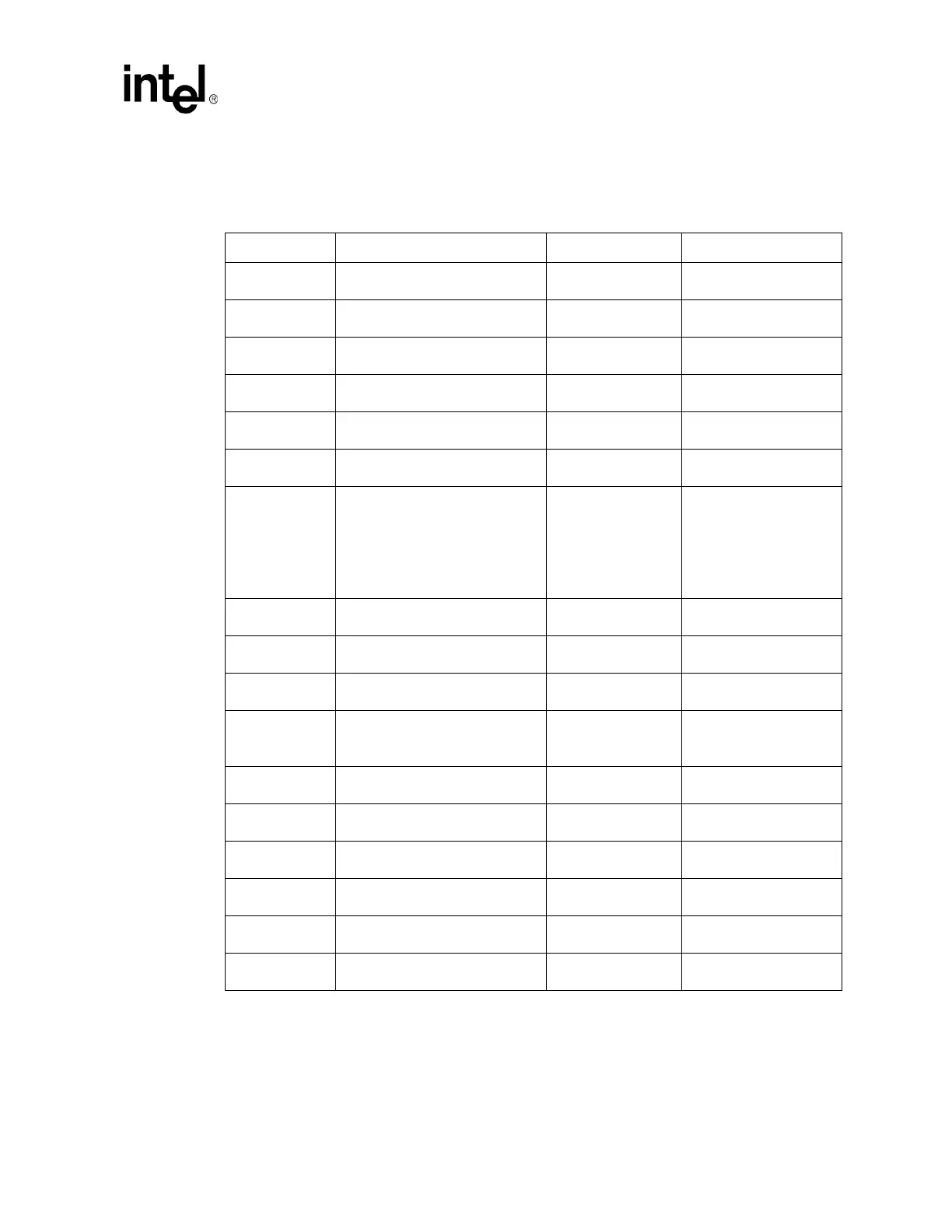

12.4.11 UART Checklist

Table 142. UART Checklist

Checklist Items Recommendations Interface Not Used Reason/Impact

SIU0_CTS# No extra pull-ups needed

May leave as no

connect

SIU1_CTS# No extra pull-ups needed

May leave as no

connect

Internal Pull-up

(15 K

Ω − 35 KΩ)

SIU0_DCD# No extra pull-ups needed

May leave as no

connect

SIU1_DCD# No extra pull-ups needed

May leave as no

connect

Internal Pull-up

(15 K

Ω − 35 KΩ)

SIU0_DSR# No extra pull-ups needed

May leave as no

connect

SIU1_DSR# No extra pull-ups needed

May leave as no

connect

Internal Pull-up

(15 K

Ω − 35 KΩ)

SIU0_DTR# No extra pull-ups needed

May leave as no

connect

Strap Function: TOP Swap

(See the 6300ESB EDS

for more information)

Pull-down to GND to use

TOP Swap function. Value

depends on platform

specifics.

SIU1_DTR# No extra pull-ups needed

May leave as no

connect

Internal Pull-up

(15 K

Ω − 35 KΩ)

SIU0_RI# No extra pull-ups needed

May leave as no

connect

SIU1_RI# No extra pull-ups needed

May leave as no

connect

Internal Pull-up

(15 K

Ω − 35 KΩ)

SIU0_RTS# No extra pull-ups needed

May leave as no

connect

Driven by the 6300ESB

Do NOT pull down this

signal.

SIU1_RTS# No extra pull-ups needed

May leave as no

connect

Internal Pull-up

(15 K

Ω − 35 KΩ)

SIU0_RXD No extra pull-ups needed

May leave as no

connect

SIU1_RXD No extra pull-ups needed

May leave as no

connect

Internal Pull-up

(15 K

Ω − 35 KΩ)

SIU0_TXD No extra pull-ups needed

May leave as no

connect

SIU1_TXD No extra pull-ups needed

May leave as no

connect

Internal Pull-up

(15 K

Ω − 35 KΩ)

UART_CLK

Recommend a 48 MHz clock

source

May leave as no

connect

See Section 9.12

Loading...

Loading...