RL78/F13, F14 CHAPTER 16 SERIAL INTERFACE IICA

R01UH0368EJ0210 Rev.2.10 1036

Dec 10, 2015

16.3.9 Port output mode register (POM6)

This register sets the output mode of P60 to P63 in 1-bit units.

N-ch open drain output (EVDD0 tolerance) mode can be selected for the SCLA0 and SDAA0 pins during I

2

C

communication.

When using the P62/SCLA0 pin as clock I/O and the P63/SDAA0 pin as serial data I/O, set POM62 and POM63 to 1.

Set the IICE0 bit (bit 7 of IICA control register 00 (IICCTL00)) to 1 before setting the output mode because the

P62/SCLA0 and P63/SDAA0 pins output a low level (fixed) when the IICE0 bit is 0.

The POM6 register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

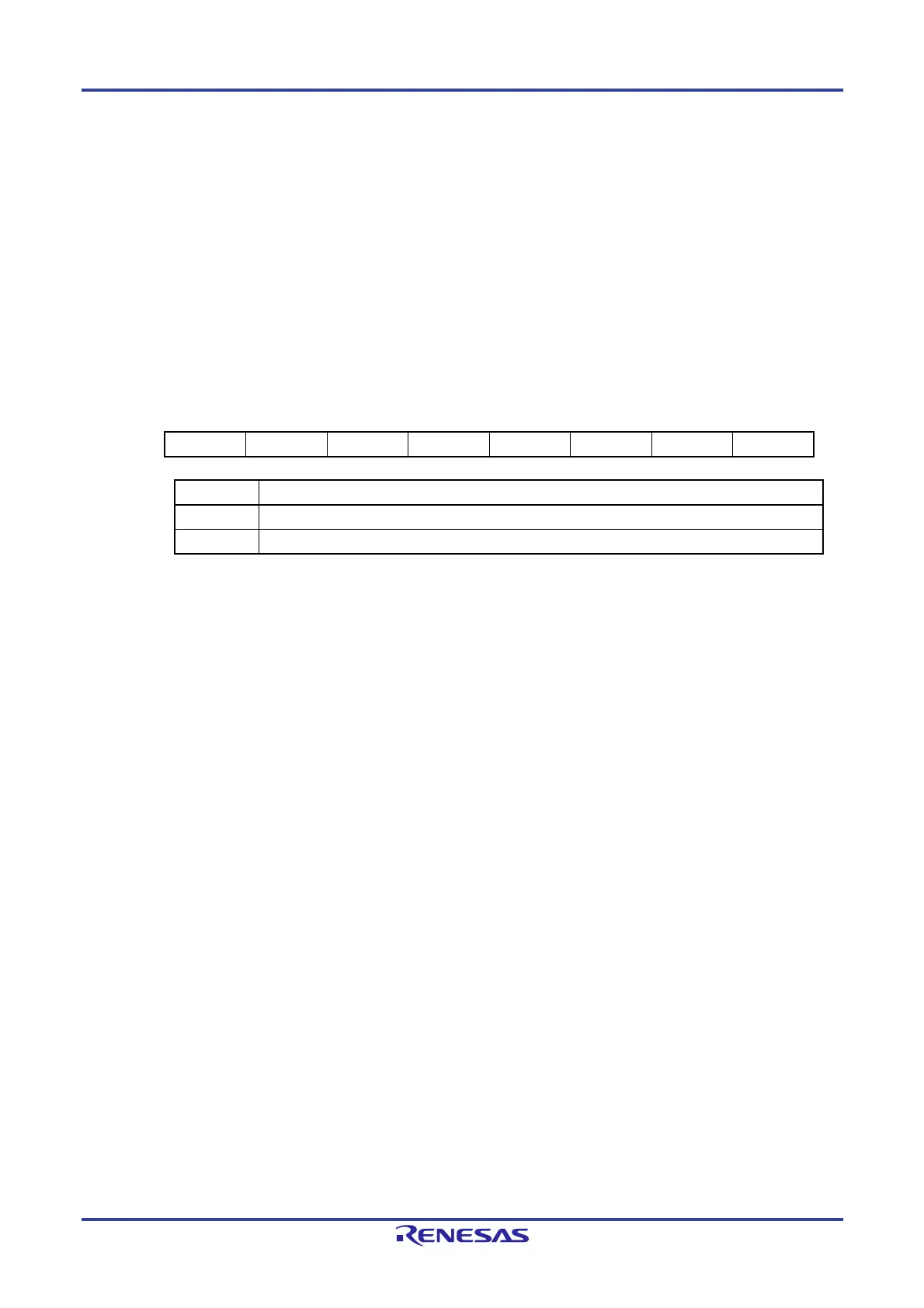

Figure 16-13. Format of Port Output Mode Register 6 (POM6)

Address: F0056H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

POM6 0 0 0 0 POM63 POM62 POM61 POM60

POMmn P6n pin output mode selection (n = 0 to 3)

0 Normal output mode

1 N-ch open-drain output (EVDD0 tolerance) mode

Caution POM62 and POM63 are used for the IICA serial interface.

Loading...

Loading...