RL78/F13, F14 CHAPTER 14 COMPARATOR (RL78/F14 Only)

R01UH0368EJ0210 Rev.2.10 788

Dec 10, 2015

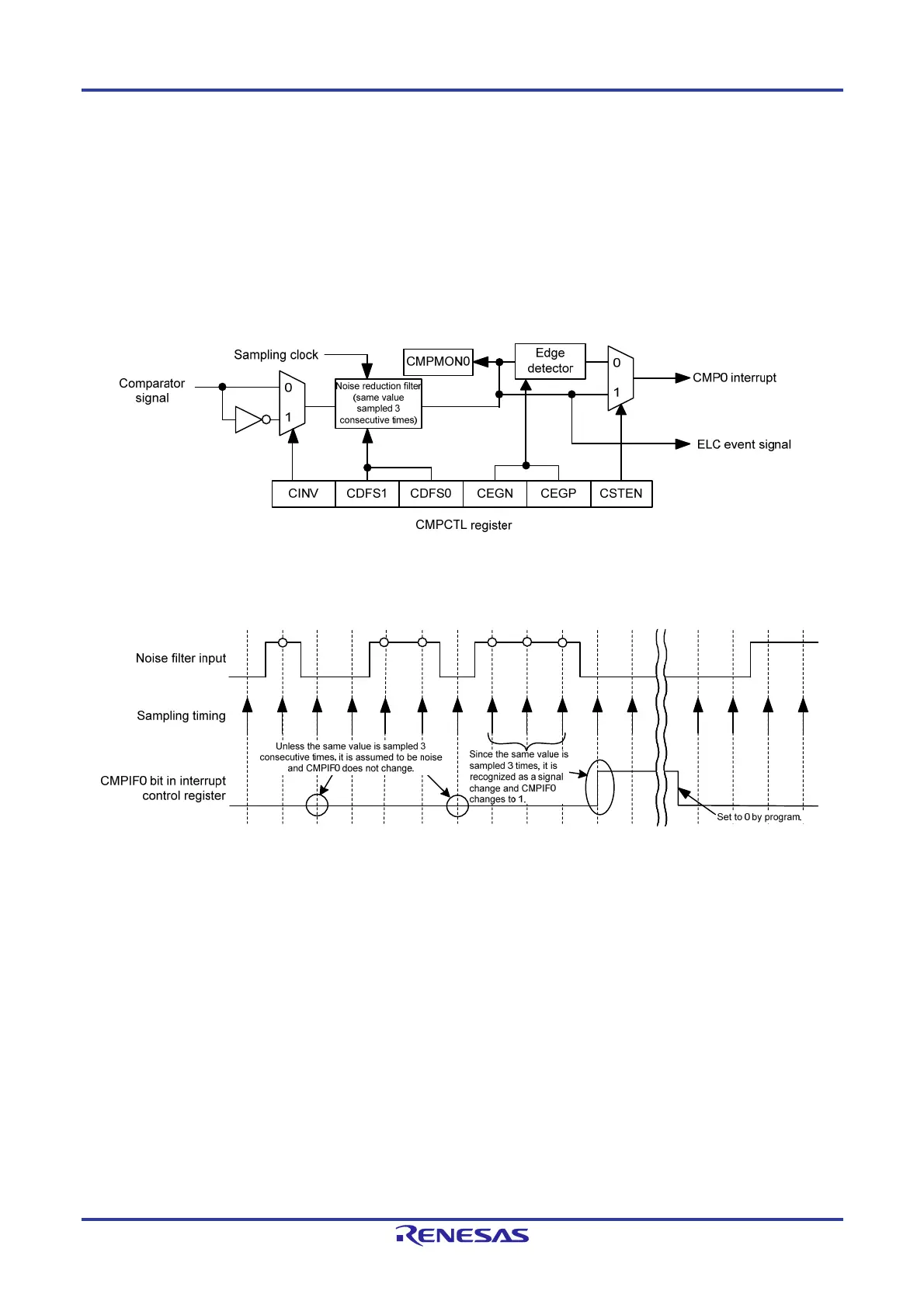

14.3.1 Noise Filter

The comparator contains a noise filter. The sampling clock can be selected by bits CDFS1 and CDFS0 in the CMPCTL

register.

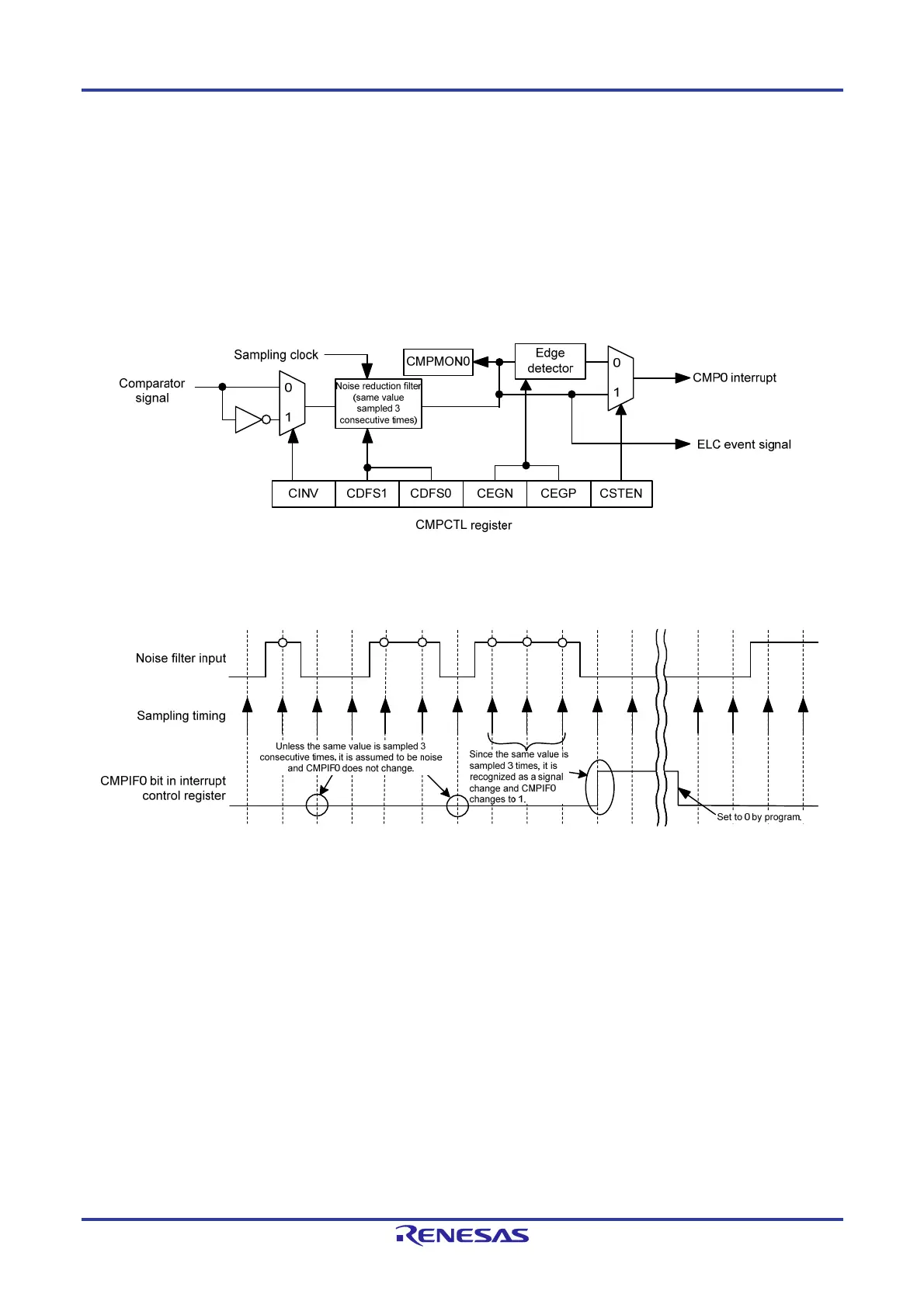

The comparator signal is sampled every sampling clock and if the same value is sampled three times, the noise filter

output at the next sampling clock cycle is used as the comparator output.

Figure 14-11 shows the configuration of the noise filter and edge detector and figure 14-12 shows an example of noise

filter and interrupt operation.

Figure 14-11. Noise Filter and Edge Detection Configuration

Figure 14-12. Noise Filter and Interrupt Operation Example

Caution The above operation example applies when bits CDFS1 and CDFS0 in the CMPCTL register is 01B, 10B,

or 11B (noise filter used).

Loading...

Loading...