RL78/F13, F14 CHAPTER 26 VOLTAGE DETECTOR

R01UH0368EJ0210 Rev.2.10 1561

Dec 10, 2015

CHAPTER 26 VOLTAGE DETECTOR

26.1 Functions of Voltage Detector

The voltage detector (LVD) has the following functions.

The LVD circuit compares the supply voltage (V

DD) with the detection voltage (VLVDH, VLVDL), and generates an internal

reset or internal interrupt signal.

The detection level for the power supply detection voltage (V

LVDH, VLVDL) can be selected by using the option byte as

one of 14 levels (For details, see CHAPTER 29 OPTION BYTE).

Operable in STOP mode.

The following three operation modes can be selected by using the option byte.

(a) Interrupt & reset mode (option byte LVIMDS1, LVIMDS0 = 1, 0)

For the two detection voltages selected by the option byte 000C1H/020C1H, the high-voltage detection level (V

LVDH)

is used for generating interrupts and ending resets, and the low-voltage detection level (V

LVDL) is used for triggering

resets.

(b) Reset mode (option byte LVIMDS1, LVIMDS0 = 1, 1)

The detection voltage (V

LVD) selected by the option byte 000C1H/020C1H is used for triggering and ending resets.

(c) Interrupt mode (option byte LVIMDS1, LVIMDS0 = 0, 1)

The detection voltage (V

LVD) selected by the option byte 000C1H/020C1H is used for generating interrupts/reset

release.

Two detection voltages (V

LVDH, VLVDL) can be specified in the interrupt & reset mode, and one (VLVD) can be specified in

the reset mode and interrupt mode.

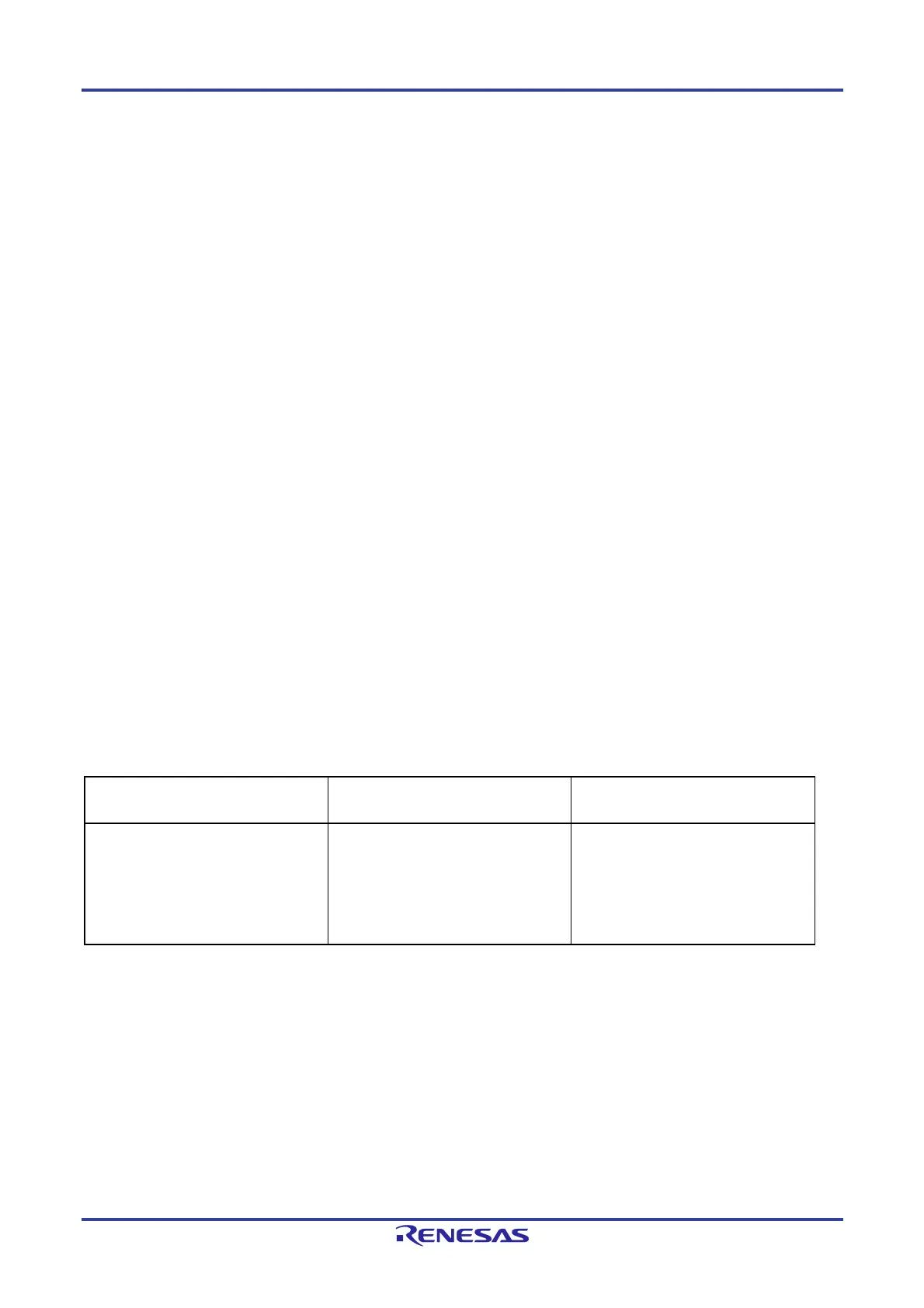

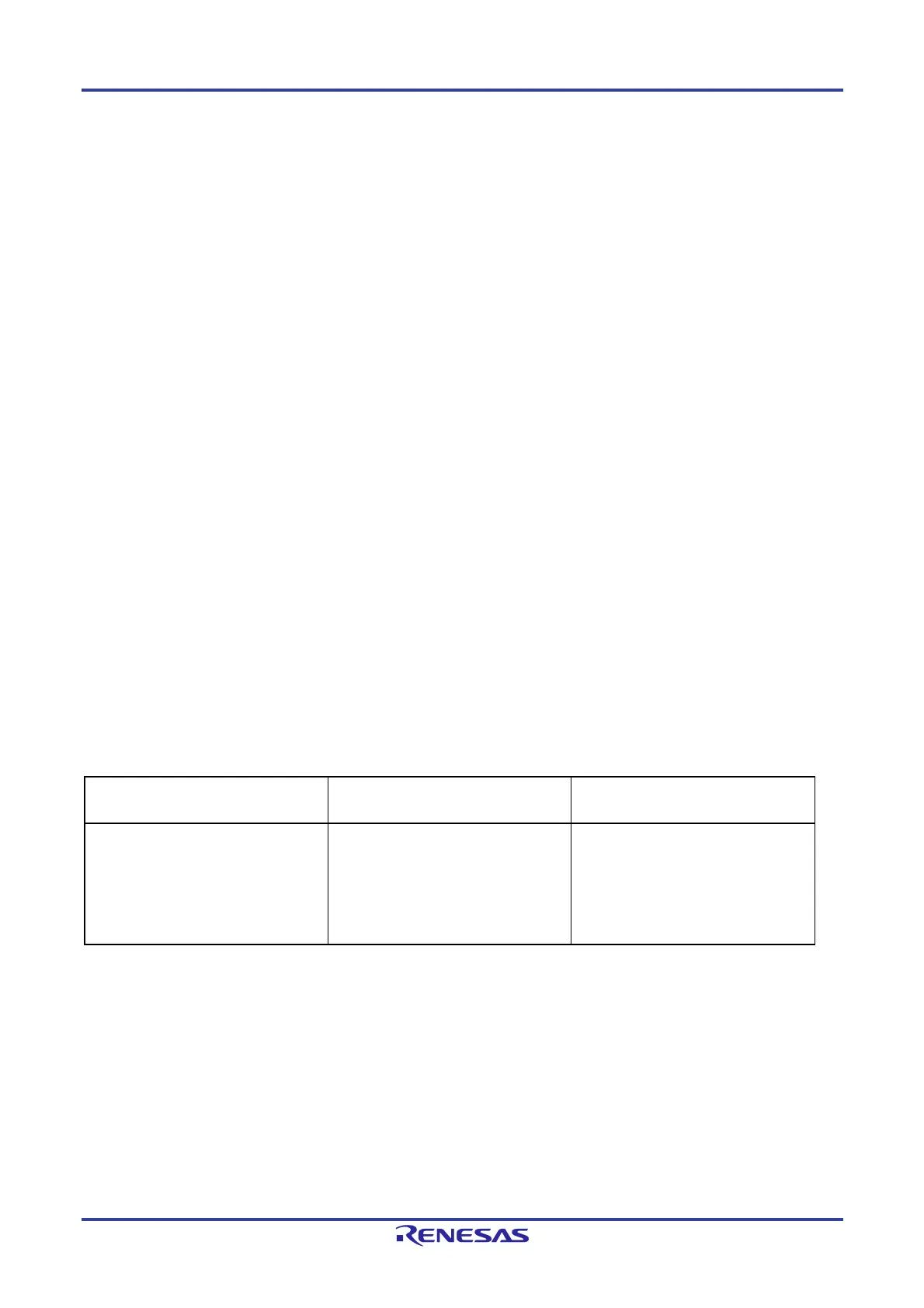

The reset and interrupt signals are generated as follows according to the option byte (LVIMDS0, LVIMDS1) selection.

Interrupt & reset mode

(LVIMDS1, LVIMDS0 = 1, 0)

Reset mode

(LVIMDS1, LVIMDS0 = 1, 1)

Interrupt mode

(LVIMDS1, LVIMDS0 = 0, 1)

Generates an internal interrupt signal

when V

DD < VLVDH, and an internal reset

when V

DD < VLVDL.

Releases the reset signal when V

DD

V

LVDH.

Generates an internal reset signal when

V

DD < VLVD and releases the reset signal

when V

DD VLVD.

Generates an internal interrupt signal

when V

DD drops lower than VLVD (VDD <

V

LVD) or when VDD becomes VLVD or

higher (V

DD VLVD).

Releases the reset signal when V

DD

V

LVD at power on.

While the voltage detector is operating, whether the supply voltage is more than or less than the detection level can be

checked by reading the voltage detection flag (LVIF: bit 0 of the voltage detection register (LVIM)).

Bit 0 (LVIRF) of the reset control flag register (RESF) is set to 1 if reset occurs. For details of the RESF register, see

CHAPTER 24 RESET FUNCTION.

Loading...

Loading...