RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1242

Dec 10, 2015

17.5.4 Status

In UART mode, the LIN/UART module can detect five types of statuses.

Two statuses, successful UART buffer transmission and error detection, can generate interrupt requests.

Table 17-26 shows the types of statuses available in UART mode.

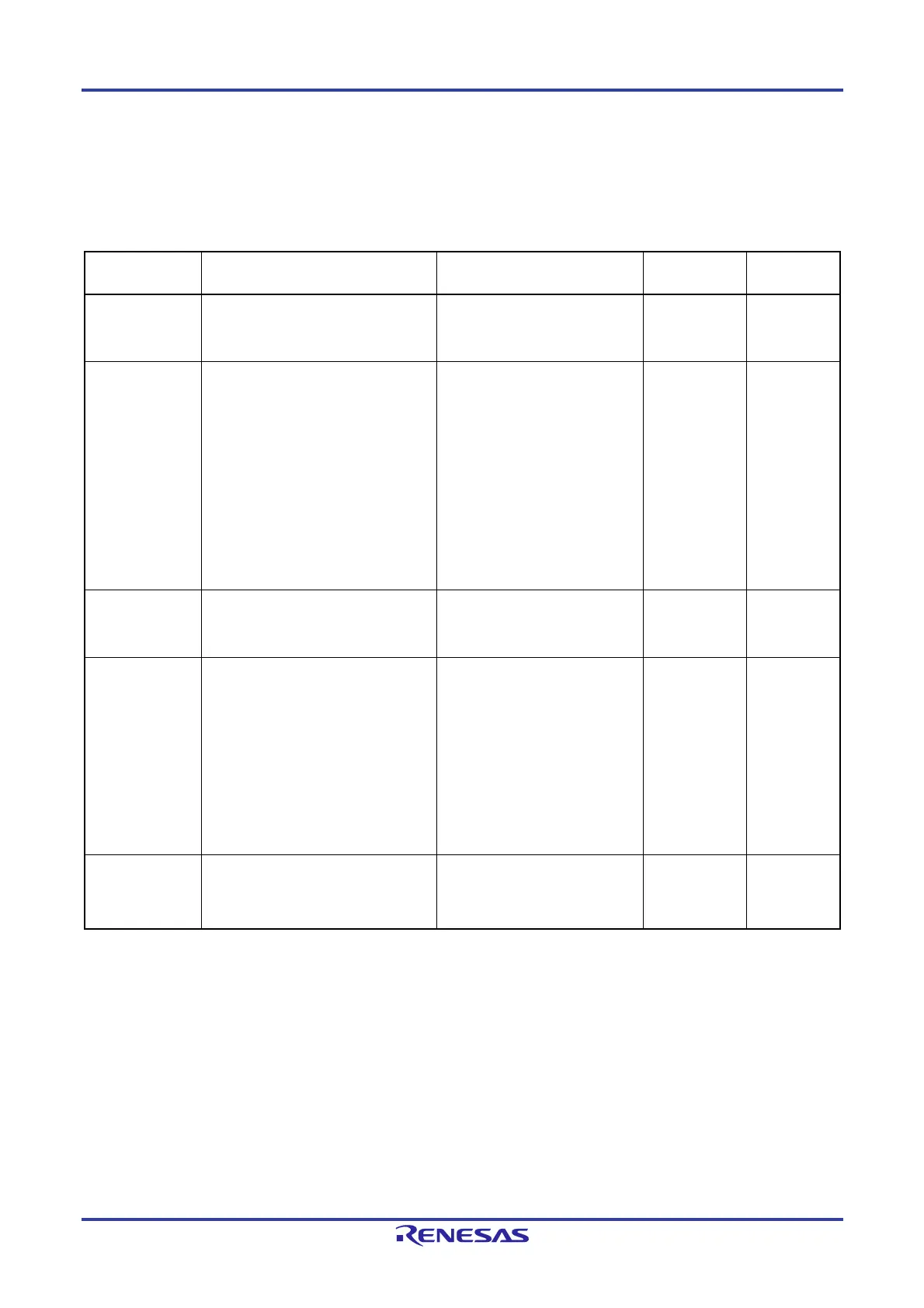

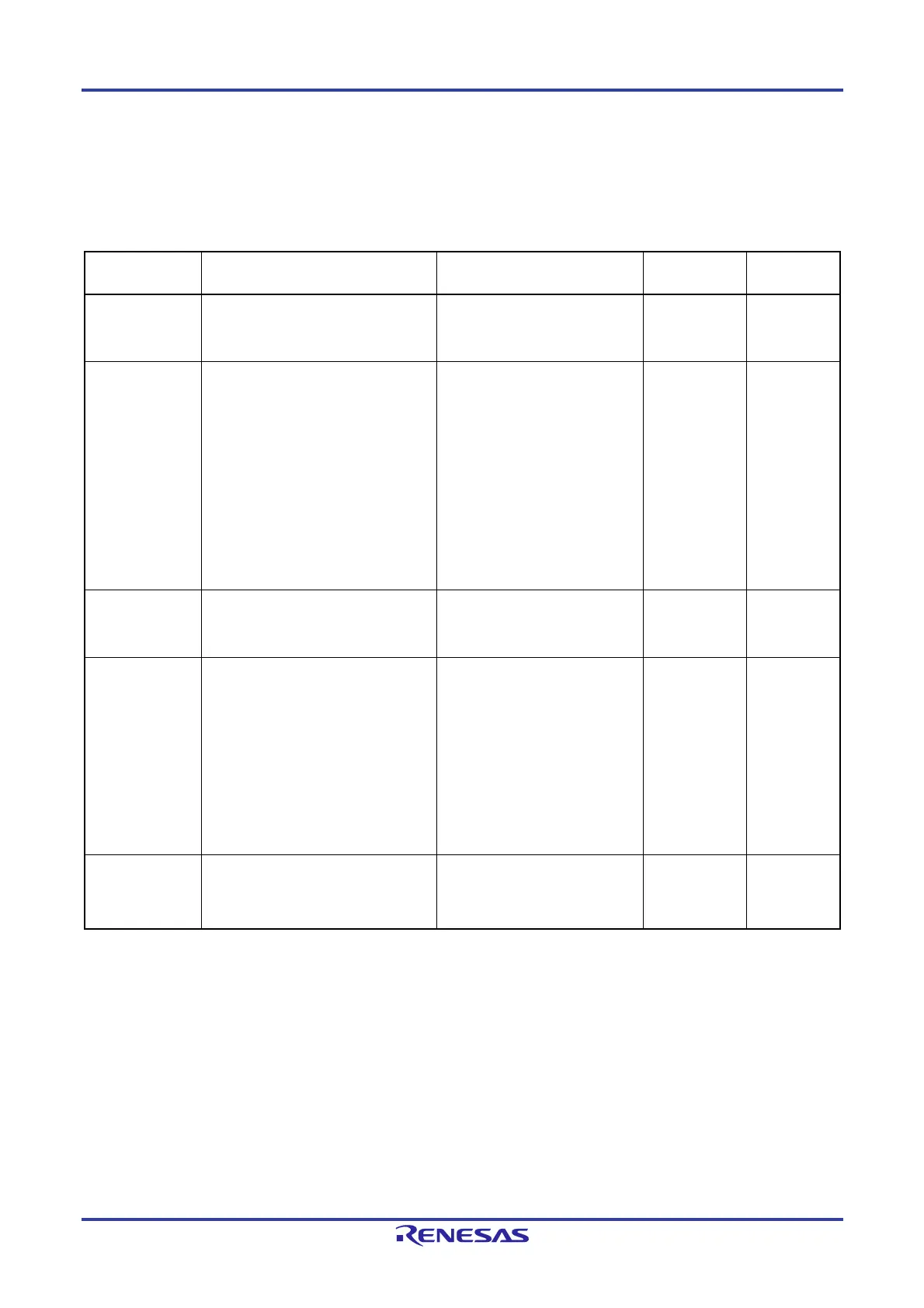

Table 17-26.

Types of Statuses in UART Mode

Status Status set condition Status clear condition

Corresponding

bit

Interrupt

Reset After the OM0 bit in the LCUCn register

is set to not-LIN–reset-mode, if actually

the LIN/UART module is cleared from

LIN reset mode.

After the OM0 bit in the LCUCn

register is set to LIN reset mode, if

actually the LIN/UART module

enters LIN reset mode.

OMM0 bit in

LMSTn register

Not available

Successful UART

buffer

transmission

The transmission of the last data of

data equal to the length set in the

MDL bits in the LDFCn register is

started while the UTIGTS bit in the

LUORn1 register is 0 (transmission

interrupt is generated at the start of

transmission).

The transmission of data equal to

the length set in the MDL bits in the

LDFCn register is completed while

the UTIGTS bit in the LUORn1

register is 1 (transmission interrupt

is generated at the completion of

transmission).

When cleared by software

After transition to LIN reset

mode

FTC flag in

LSTn register

Available

Error detection If any of the UPER flag, IDMT flag,

EXBT flag, FER flag, OER flag, and

BER flags in the LESTn register turns 1

(error detected).

When cleared by software

Note

After transition to LIN reset

mode

ERR flag in

LSTn register

Available

Transmission

status

When data is written to the LUTDRn

or LUWTDRn register.

When a 1 is written to the RTS bit in

the LTRCn register.

The transmission of the data

set in the LUTDRn or

LUWTDRn register is

complete, but another

transmission data item is not

set

The transmission of the data in

the UART buffer is complete,

and the RTS bit in the LTRCn

register is cleared

After transition to LIN reset

mode

UTS flag in

LSTn register

Not available

Reception status

When a start bit is detected. When a sampling point for stop

bits is detected

After transition to LIN reset

mode

URS flag in

LSTn register

Not available

Note Writing a 0 to the UPER, IDMT, EXBT, FET, OER, and BER flags in the LESTn register when the LIN reset mode

is being canceled turns the ERR flag in the LSTn register to 0.

Loading...

Loading...