RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1251

Dec 10, 2015

17.7 Baud Rate Generator

The prescaler clock is obtained by frequency-dividing the LIN communication clock source by the prescaler, and the LIN

system clock (f

LIN) is obtained by frequency-dividing the prescaler clock by the baud rate generator. The clock obtained by

frequency-dividing the LIN system clock (f

LIN) by the number of samples is the baud rate. The reciprocal of this baud rate is

called the bit time (Tbit).

The LIN/UART module has two kinds of baud rate generators. The baud rate generators switch over according to the mode

used.

17.7.1 LIN Master Mode

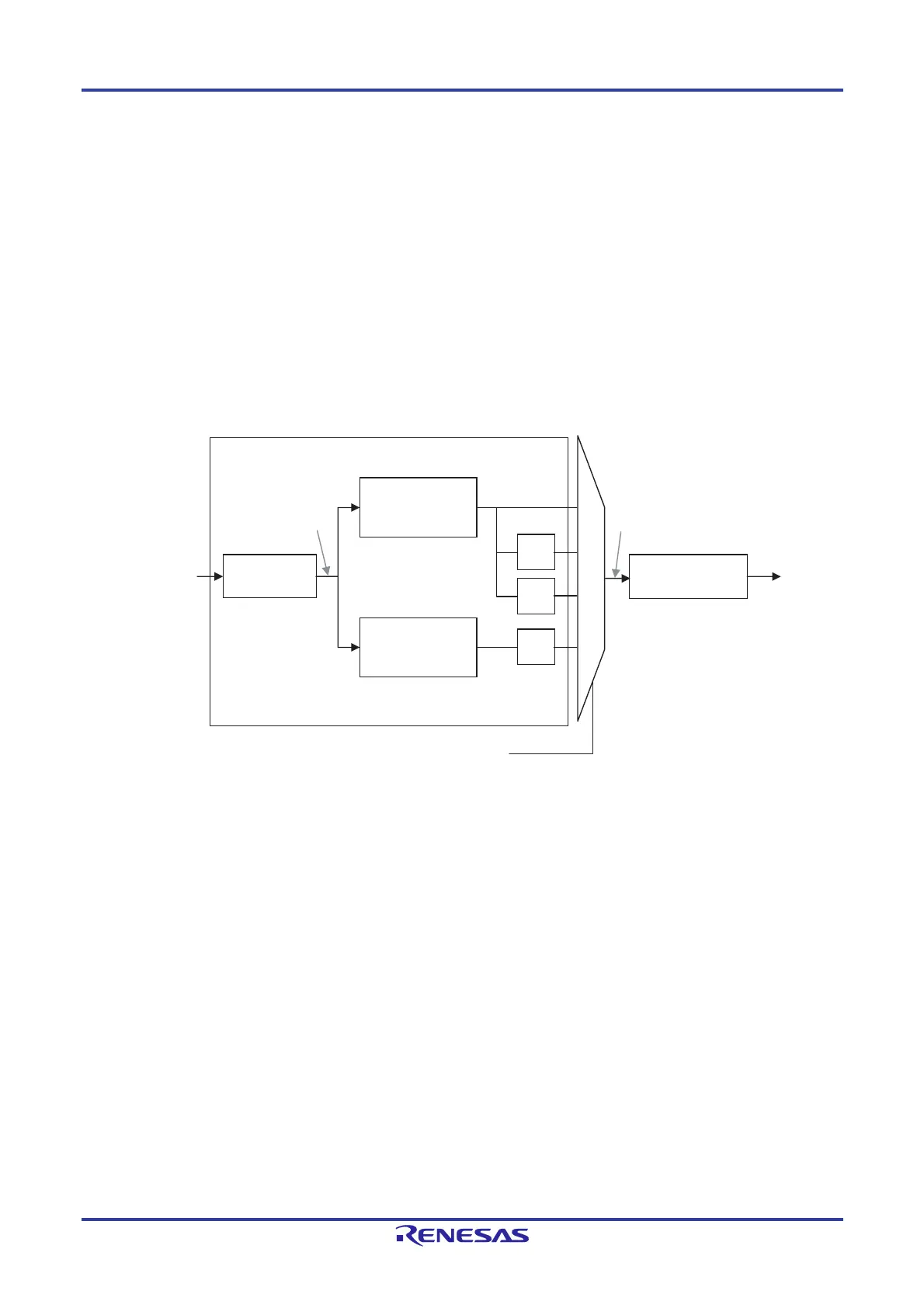

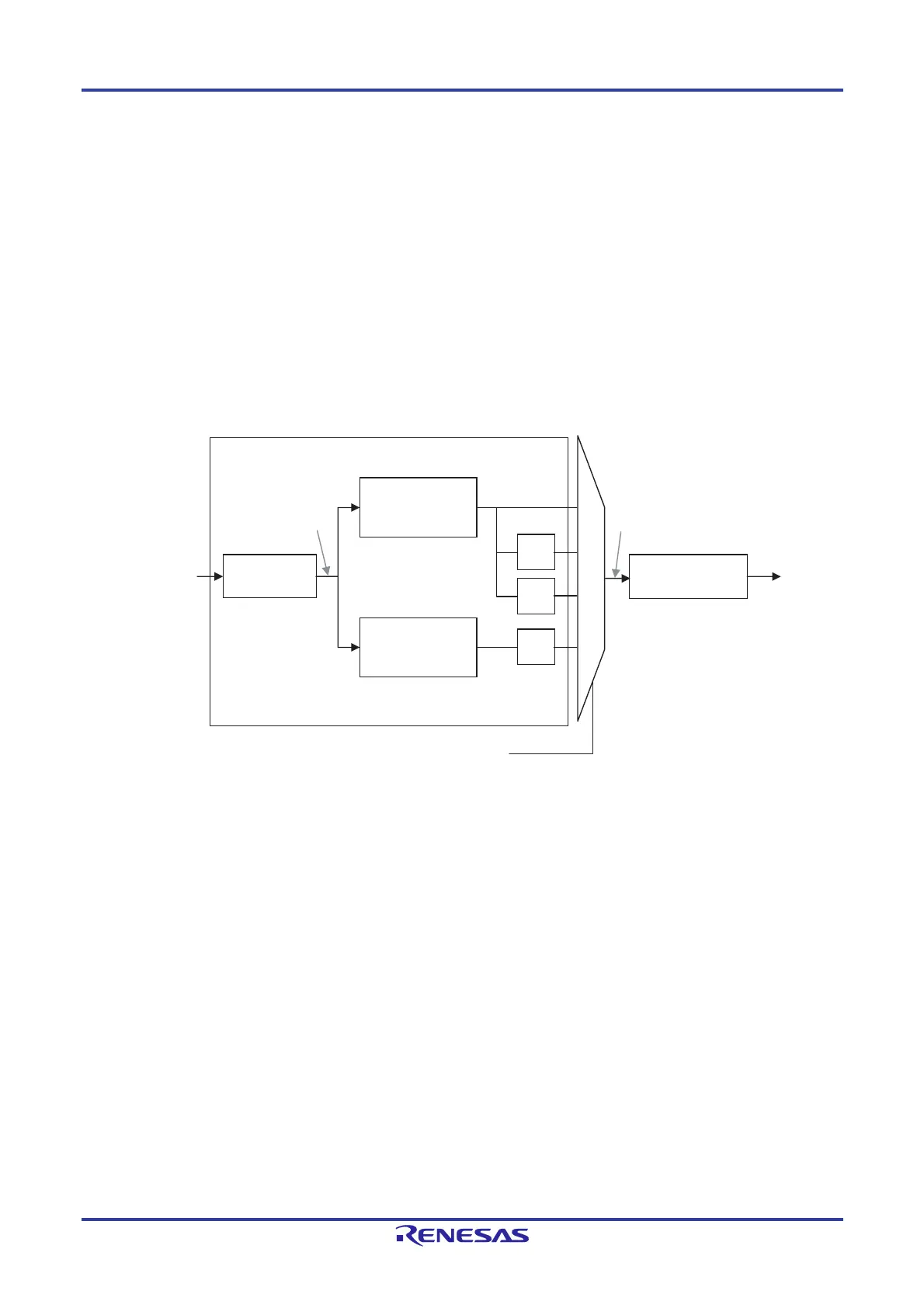

Figure 17-41 shows a block diagram of baud rate generation in LIN master mode.

Figure 17-41. Block Diagram of Baud Rate Generation in LIN Master Mode

Set the LIN communications clock source as follows.

LIN communications clock source = f

CLK

Note 1

In the range from 4 MHz to 32 MHz

Note 1. When the timeout error detection is not used, the f

MX clock is selectable as the LIN communication clock source.

In that case, set at least 1.2 times the frequency of the LIN communication clock source to the CPU/peripheral

hardware clock(fCLK).

By setting the LBRPn0 register so that fa is 307200 Hz (= 19200 16), the resulting bit rates are fa = 19200 16, fb = 9600

16 and fc = 2400 16. These bit rates are frequency-divided by 16 in the bit timing generator, enabling bit rates of 19200

bps, 9600 bps and 2400 bps to be generated. Also, by setting the LBRPn1 register so that fd is 166672 Hz (= 10417 16),

the resulting bit rate is fd = 10417 16. This bit rate is frequency-divided by 16 in the bit timing generator, enabling 10417

bps to be generated.

Table 17-28 shows examples of baud rate (19200, 10417, 9600, and 2400 bps) generation for each LIN communication

clock source frequency, and also the corresponding errors.

Prescaler

(LPRS[2:0] bits)

LIN baud rate

prescaler 0

(LBRPn0 register)

LIN communication

clock source

Note 1

fa

fb

fc

fd

Bit sampling

1/16

(NSPB[3:0] bits)

Baud rate

LIN baud rate

prescaler 1

(LBRPn1 register)

1/2

1/2

1/8

LCKS[1:0] bits in LMDn register

Baud rate generator

Prescaler clock f

LIN

Note 2

Note 3

3. When the value in the LBRPn1 register is M (M = 0 to 255), the clock frequency is divided by M+1.

2. When the value in the LBRPn0 register is N (N = 0 to 255), the clock frequency is divided by N+1.

Notes 1. For the LIN communication clock source, refer to CHAPTER 5 CLOCK GENERATOR.

<R>

Loading...

Loading...