RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 406

Dec 10, 2015

5.6.4 Examples of Setting PLL Circuit

The following PLL setting procedures are described here.

Oscillating the PLL clock and setting it as the CPU clock

Stopping the PLL clock

[Register settings] Set the registers in the following order.

(1) Example of procedure for setting oscillation of PLL clock

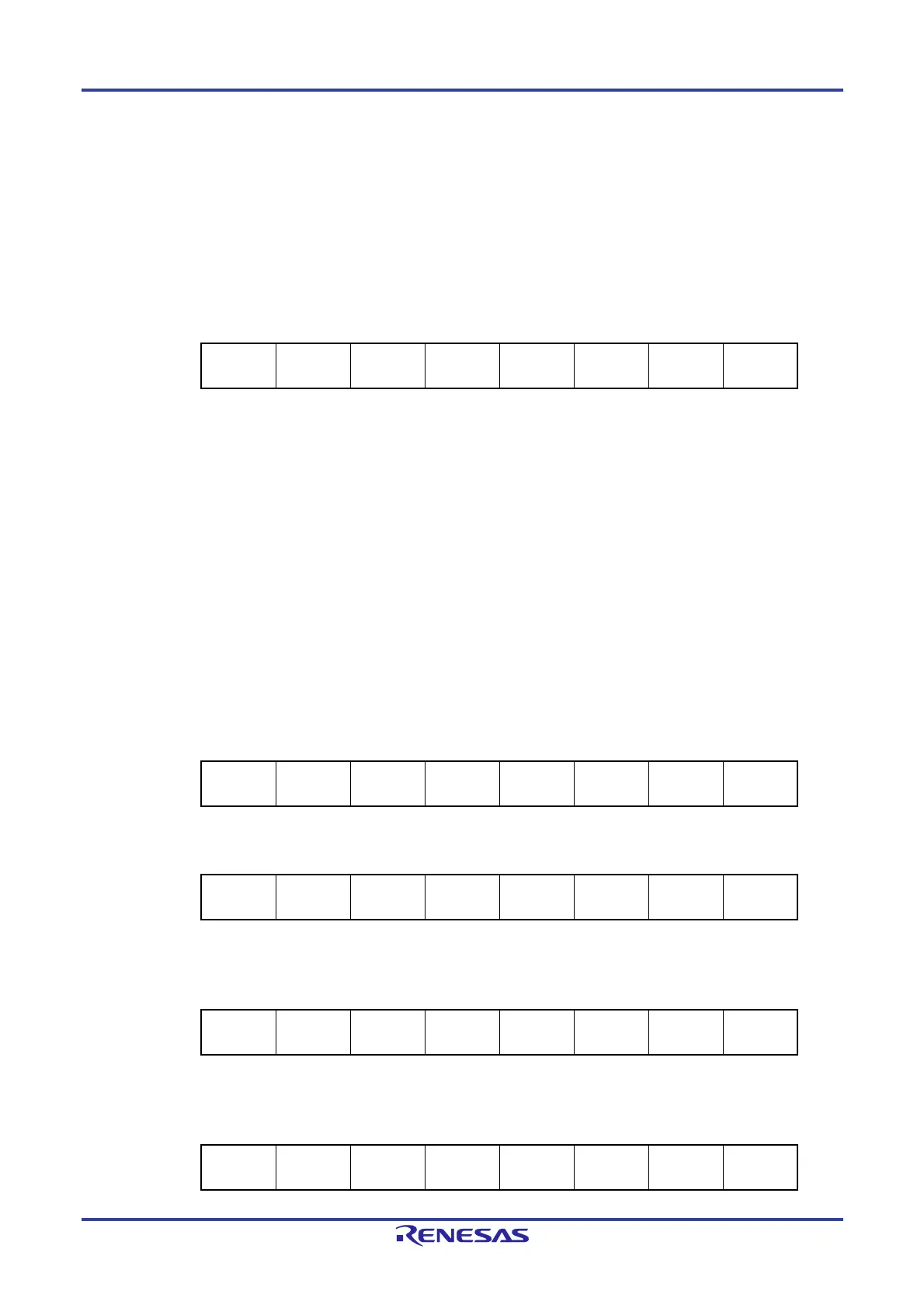

<1> Select the frequency of the PLL output clock with the PLLDIV1 bit of the PLLCTL register.

When PLL clock 32 MHz, clear the PLLDIV1 bit to 0. When PLL clock 32 MHz, set the PLLDIV1 bit to 1.

7 6 5 4 3 2 1 0

PLLCTL

LCKSEL1

0/1

LCKSEL0

0/1

PLLDIV1

0/1

PLLDIV0

0/1

0

SELPLL

0

PLLMUL

0/1

PLLON

0

<2> Set the PLL lock-up wait counter with the LCKSEL1 and LCKSEL0 bits of the PLLCTL register.

The counter for the PLL lock-up wait time is set to a period of at least 40 s. When the PLL source clock (f

MAIN) is

4 MHz, set the LCKSEL1 and LCKSEL0 bits to 01 or 10. When the PLL source clock (f

MAIN) is 8 MHz, set the

LCKSEL1 and LCKSEL0 bits to 10.

<3> Select the frequency division of the PLL clock with the PLLDIV0 bit of the PLLCTL register.

When PLLDIV0 = 0, the PLL division ratio is 2. When PLLDIV0 = 1, the PLL division ratio is 4.

<4> Select the multiplication value of the PLL clock with the PLLMUL bit of the PLLCTL register.

When PLLMUL = 0, the PLL multiplication value is 12. When PLLMUL = 1, the PLL multiplication value is 16.

<5> Wait for the selection of the PLL multiplication value to become effective. After setting the PLLMUL bit, wait for at

least 1 s.

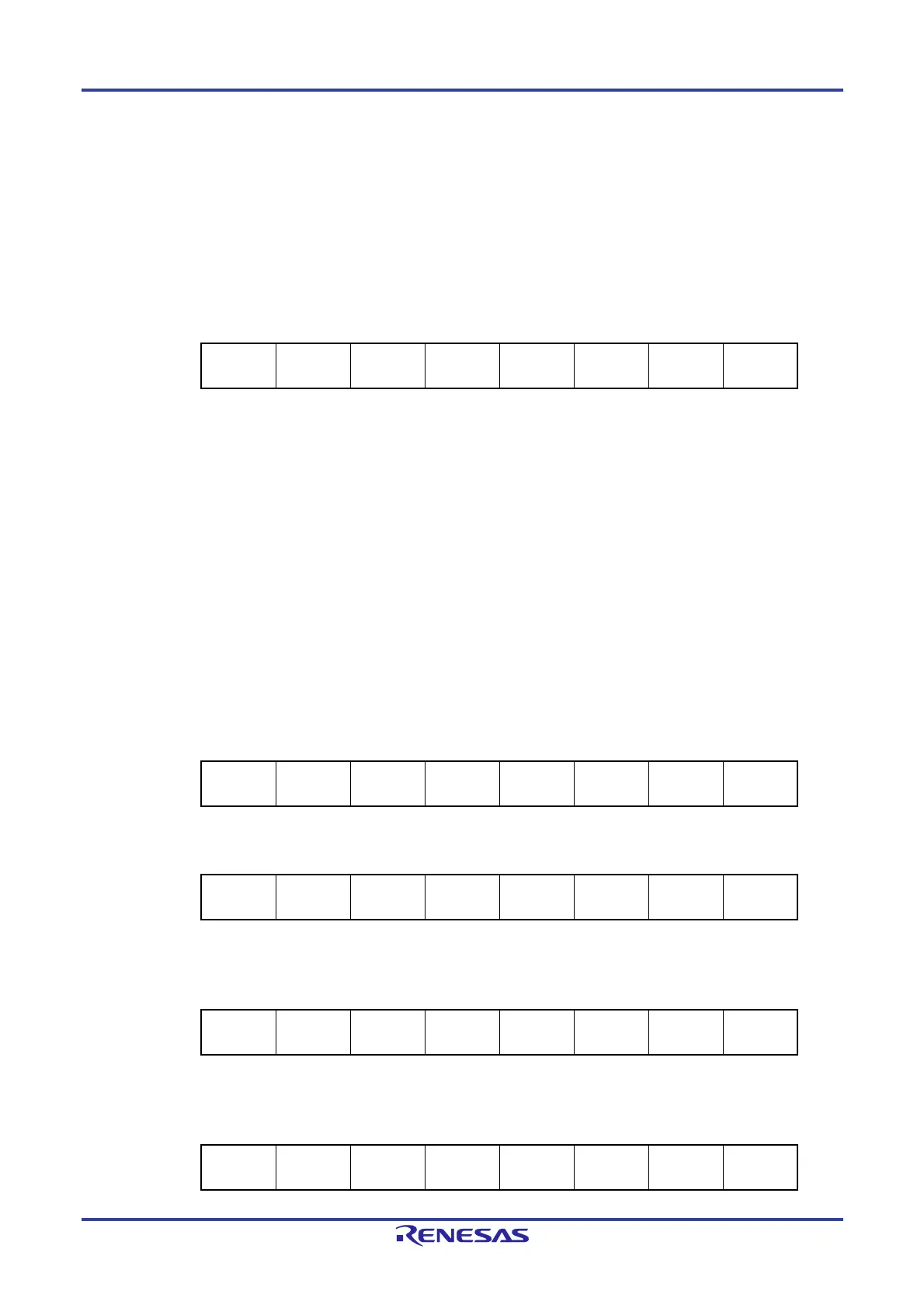

<6> Set the PLLON bit of the PLLCTL register to 1 to start oscillation of the PLL clock.

7 6 5 4 3 2 1 0

PLLCTL

LCKSEL1

0/1

LCKSEL0

0/1

PLLDIV1

0/1

PLLDIV0

0/1

0

SELPLL

0

PLLMUL

0/1

PLLON

1

<7> Confirm that the PLL circuit is locked (LOCK = 1) with the LOCK bit of the PLLSTS register.

7 6 5 4 3 2 1 0

PLLSTS

LOCK

1

0

0

0

0

0

0

0

<8> Set the PLL clock between 1 MHz and 32 MHz with the MDIV bits of the MDIV register.

Example: To select f

MP/2, set the following value.

7 6 5 4 3 2 1 0

MDIV

0

0

0

0

0

MDIV2

0

MDIV1

0

MDIV0

1

<9> Select the PLL clock mode with the SELPLL bit of the PLLCTL register.

Set the SELPLL bit to 1 to select the PLL-clock-selected mode (f

MP = fPLL).

7 6 5 4 3 2 1 0

PLLCTL

LCKSEL1

0/1

LCKSEL0

0/1

PLLDIV1

0/1

PLLDIV0

0/1

0

SELPLL

1

PLLMUL

0/1

PLLON

1

Loading...

Loading...