RL78/F13, F14 CHAPTER 19 DTC

R01UH0368EJ0210 Rev.2.10 1462

Dec 10, 2015

19.4.6 Number of DTC Execution Clock Cycles

Table 19-10 lists the operations following DTC activation and required number of clock cycles for each operation.

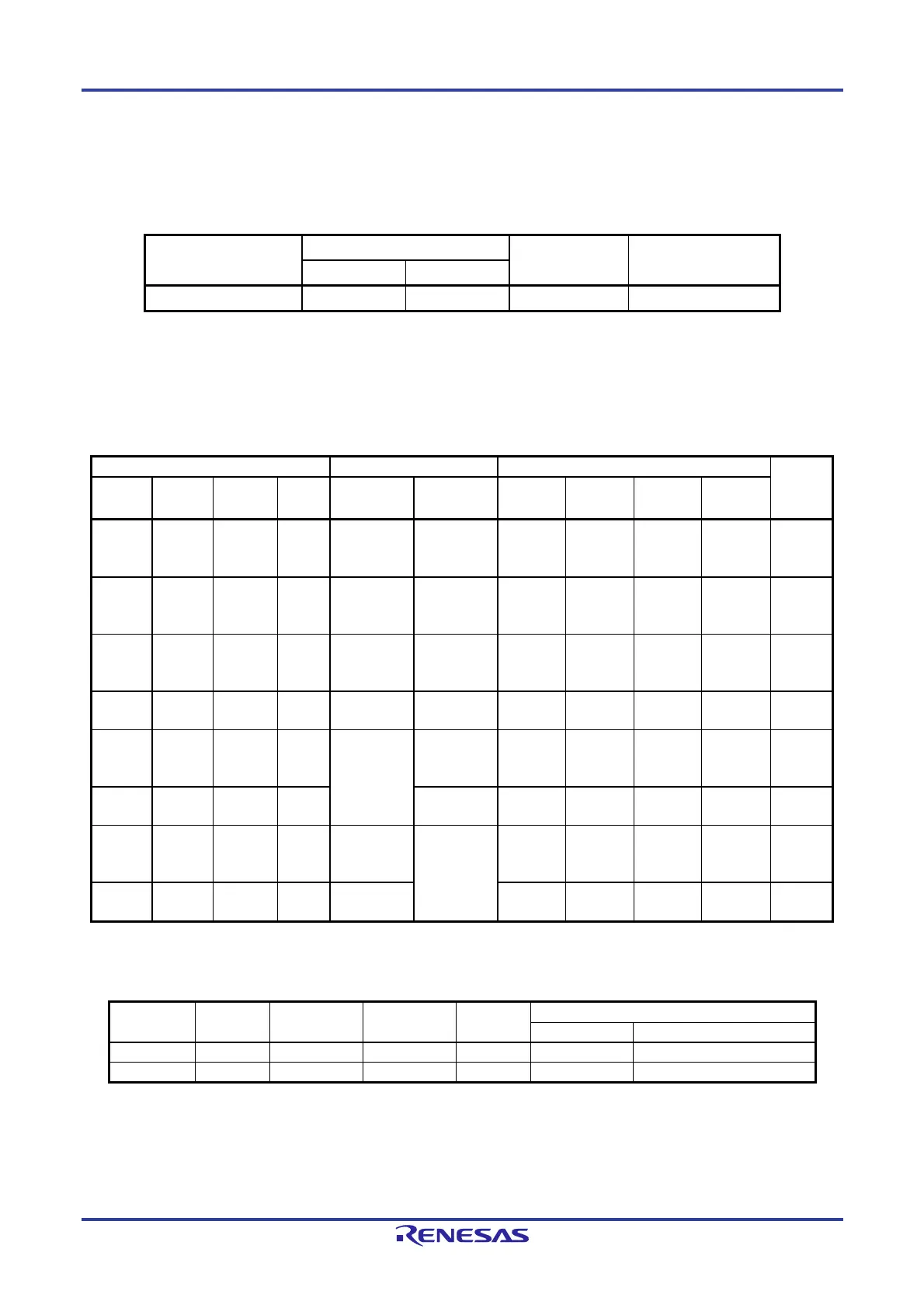

Table 19-10. Operations Following DTC Activation and Required Number of Cycles

Vector Read

Control Data

Data Read Data Write

Read Write-back

1 4 Note 1 Note 2 Note 2

Notes 1. For the number of clock cycles required for control data write-back, refer to Table 19-11 Number of Clock

Cycles Required for Control Data Write-Back Operation.

2. For the number of clock cycles required for data read/write, refer to Table 19-12 Number of Clock Cycles

Required for Data Read/Write Operation.

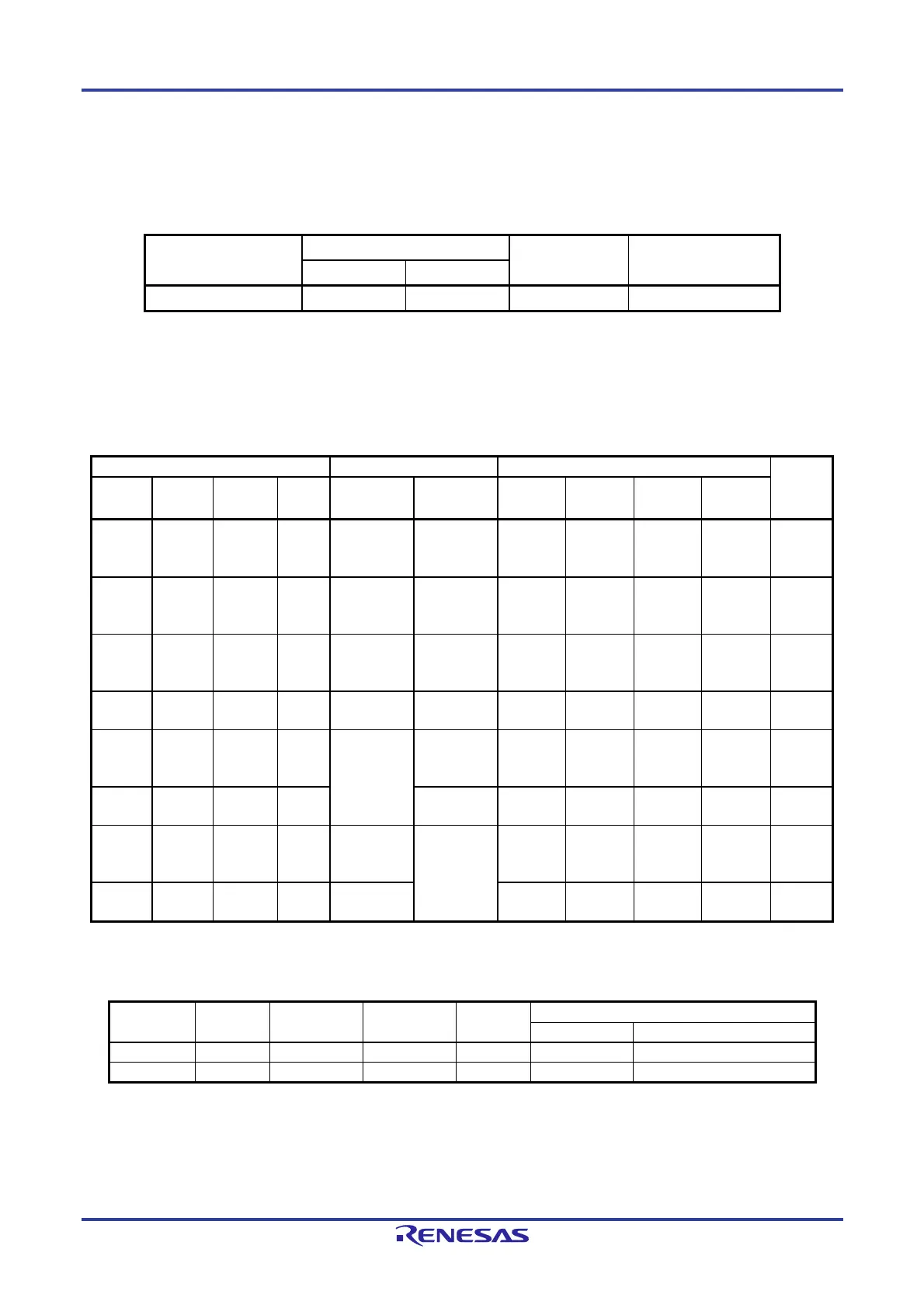

Table 19-11. Number of Clock Cycles Required for Control Data Write-Back Operation

DTCCR Register Setting Address Setting Control Register to be Written Back Number

of Clock

Cycles

DAMO

D

SAMO

D

RPTSEL

MOD

E

Source Destination

DTCCTj

Register

DTRLDj

Register

DTSARj

Register

DTDARj

Register

0 0 X 0 Fixed Fixed Written

back

Written

back

Not

written

back

Not

written

back

1

0 1 X 0 Incremente

d

Fixed Written

back

Written

back

Written

back

Not

written

back

2

1 0 X 0 Fixed Incremente

d

Written

back

Written

back

Not

written

back

Written

back

2

1 1 X 0 Incremente

d

Incremente

d

Written

back

Written

back

Written

back

Written

back

3

0 X 1 1 Repeat

area

Fixed Written

back

Written

back

Written

back

Not

written

back

2

1 X 1 1 Incremente

d

Written

back

Written

back

Written

back

Written

back

3

X 0 0 1 Fixed Repeat

area

Written

back

Written

back

Not

written

back

Written

back

2

X 1 0 1 Incremente

d

Written

back

Written

back

Written

back

Written

back

3

Remark j = 0 to 23; X: 0 or 1

Table 19-12. Number of Clock Cycles Required for Data Read/Write Operation

Operation RAM Code Flash

Memory

Data Flash

Memory

SFR 2nd SFR

No Wait State Wait States

Data read 1 2 4 1 1 1 + number of wait states

Note

Data write 1 - - 1 1 1 + number of wait states

Note

Note The number of wait states differs depending on the specifications of the register allocated to the second SFR to

be accessed.

Loading...

Loading...