RL78/F13, F14 CHAPTER 19 DTC

R01UH0368EJ0210 Rev.2.10 1459

Dec 10, 2015

19.3.5 High-Speed Transfer Operation

There are two channels for high-speed transfer. Each DTC activation source is selected by the high-speed DTC channel

select register m. When the DTC is activated by the source selected by the high-speed transfer channel, the control data

dedicated for high-speed transfer instead of the control data specified by the DTC vector address is read and transferred.

Initialize the control data area with any desired value because the control data are read.

Block transfer always transfers 1-byte data for 8-bit transfer and 2-byte data for 16-bit transfer.

Chain transfer reads and transfers the control data consecutively allocated subsequent to the control data specified by

the DTC vector address. During a chain transfer, when control data is for the source selected by the other high-speed

transfer channel, the consecutively allocated control data instead of the control data dedicated for high-speed transfer is

read and transferred.

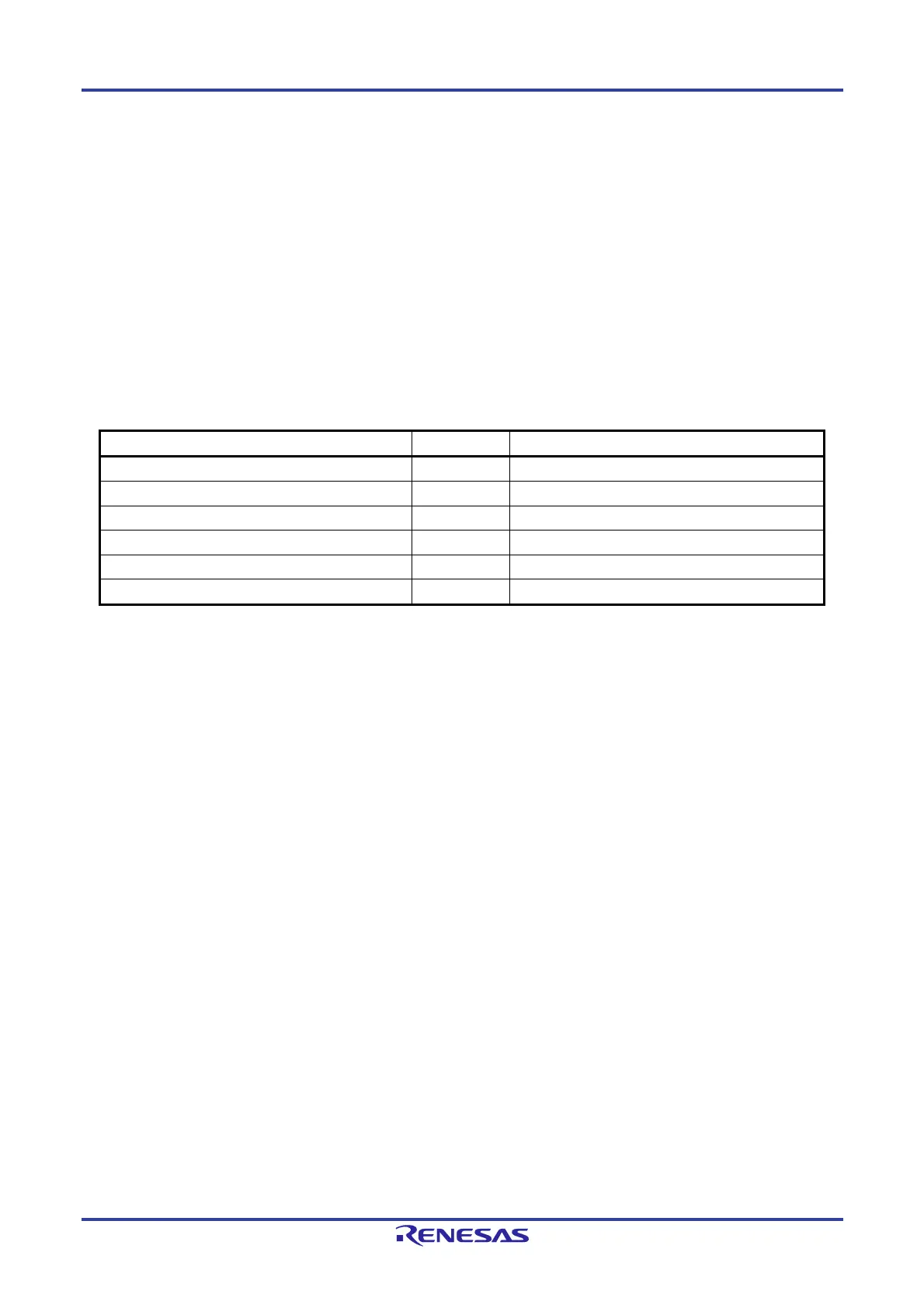

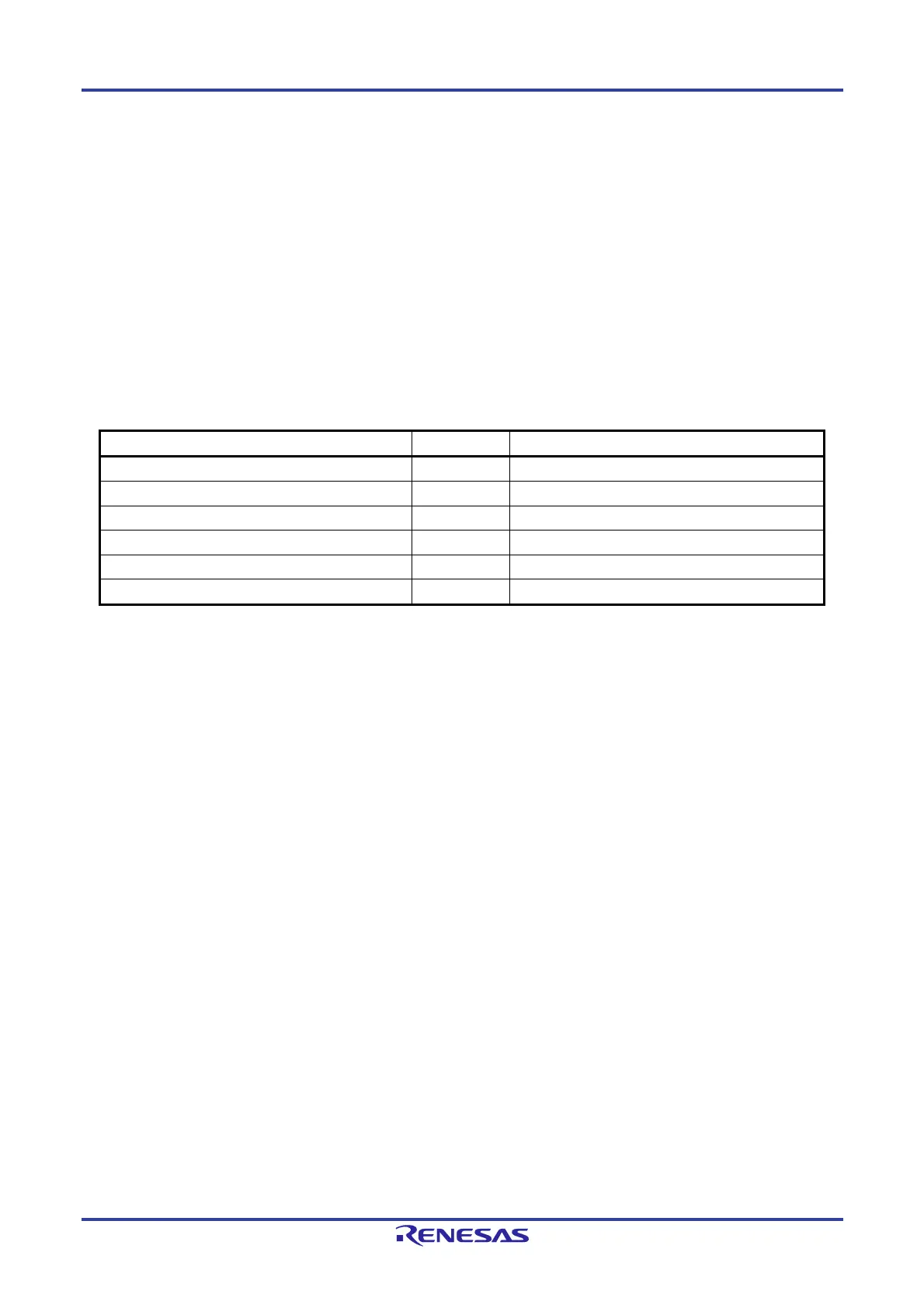

Table 19-9 shows the register functions in high-speed transfer operation.

Table 19-9. Register Functions in High-speed Transfer Mode

Register Name Symbol Function

High-speed DTC channel select register 0/1 SELHS0/1 Channel selection

High-speed DTC control register 0/1 HDTCCR0/1 Operating mode control

High-speed DTC transfer count register 0/1 HDTCCT0/1 Number of data transfers

High-speed DTC transfer count reload register 0/1 HDTRLD0/1 Initial value setting

High-speed DTC source address register 0/1 HDTSAR0/1 Data transfer source address

High-speed DTC destination address register 0/1 HDTDAR0/1 Data transfer destination address

Loading...

Loading...