RL78/F13, F14 CHAPTER 25 POWER-ON-RESET CIRCUIT

R01UH0368EJ0210 Rev.2.10 1560

Dec 10, 2015

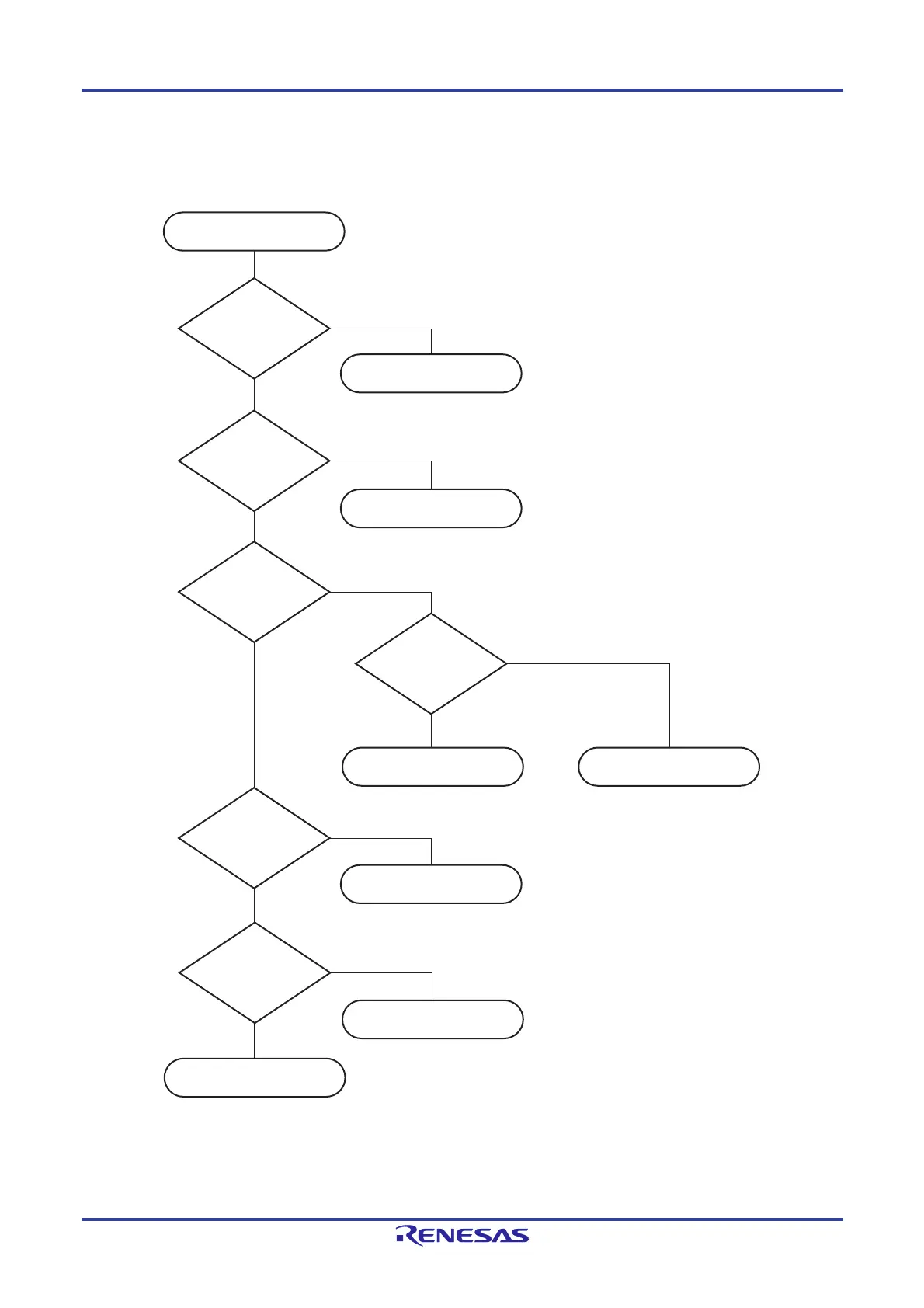

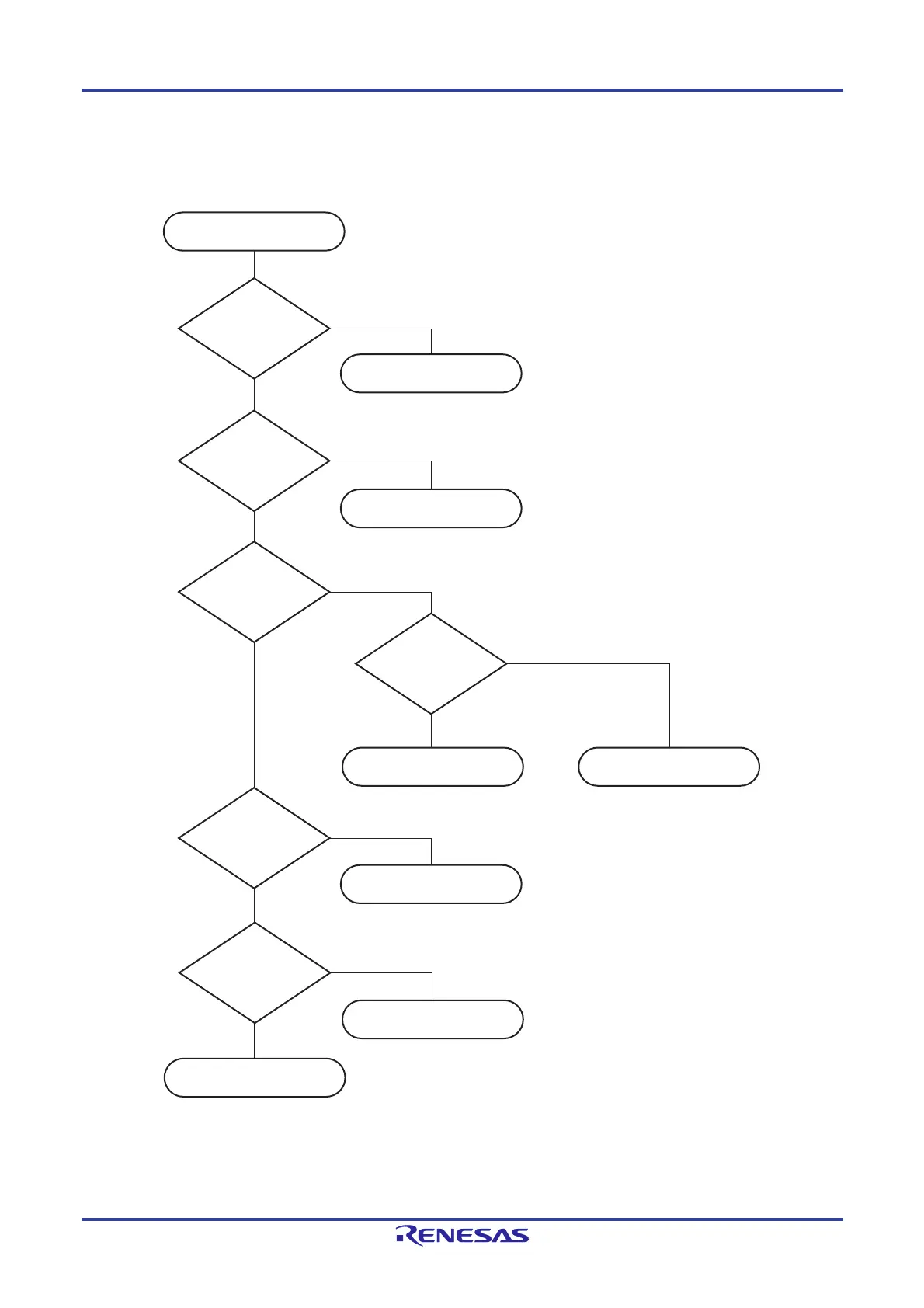

Figure 25-3. Example of Software Processing After Reset Release (2/2)

(2) Checking reset source

Note The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or on-chip

debug emulator.

Reset processing by

voltage detector

Reset processing by

watchdog timer

Reset processing by

clock monitor

Reset processing by

external reset

No

Yes

Yes

No

Check reset source

Yes

Yes

No

Yes

No

No

Yes

No

Reset processing by

illegal-memory access

Reset processing by

illegal instruction execution

Note

LVIRF of RESF

register = 1 ?

IAWRF of RESF

register = 1?

WDCLRF of RESF

register = 1 ?

TRAP of RESF

register = 1 ?

POCRES0 of

POCRES register = 0 ?

CLKRF of POCRES

register = 1 ?

Reset processing by

power-on reset circuit

Loading...

Loading...