AGP Interface Routing

R

116 Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide

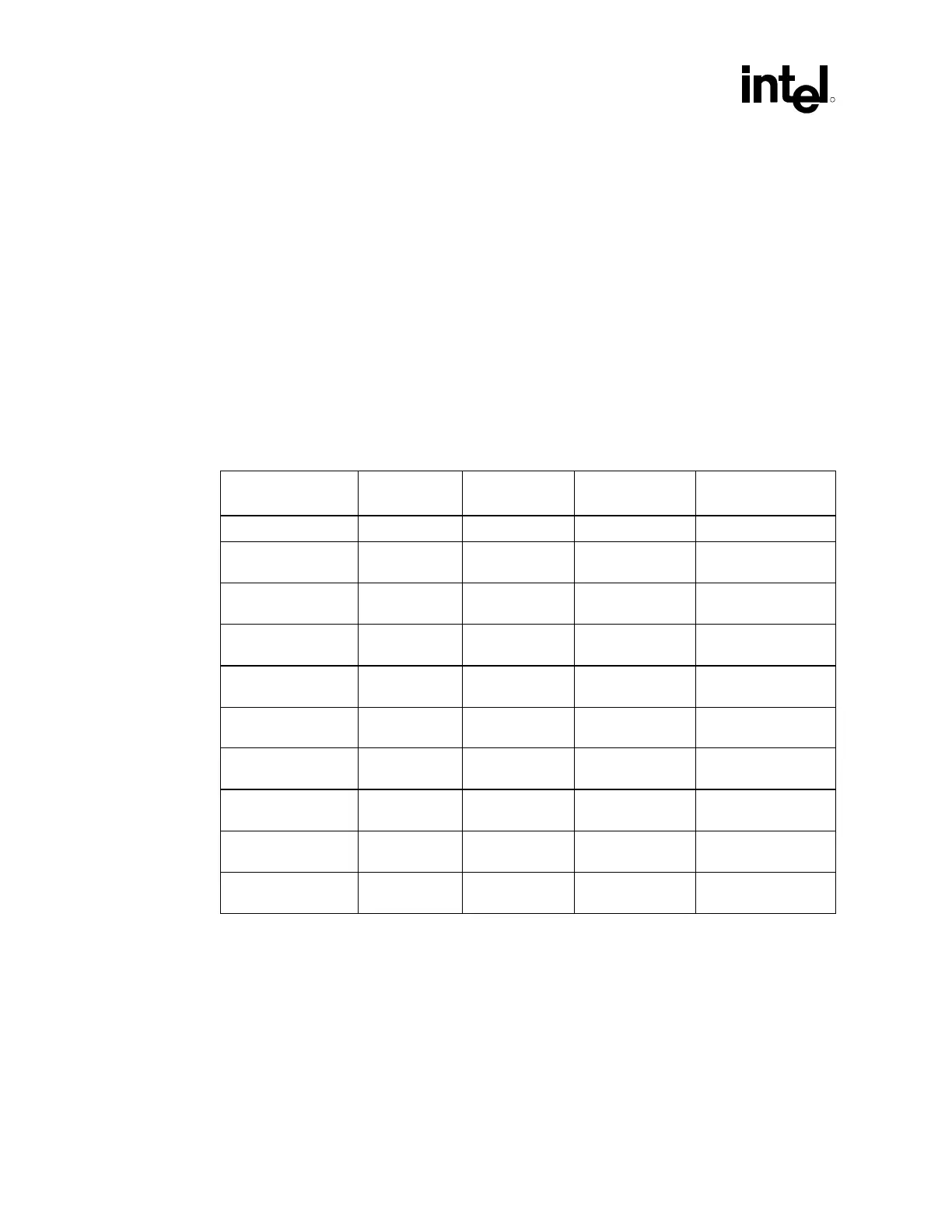

7.1.3 AGP Interfaces Trace Length Summary

The 2X/4X Timing Domain Signals can be routed with 5 mil spacing when breaking out of the

MCH. The routing must widen to the documented requirements within 0.3 inches of the MCH

package.

When matching trace length for the AGP 4X interface, all traces should be matched from the ball

of the MCH to the pin on the AGP connector. It is not necessary to compensate for the length of

the AGP signals on the MCH package.

Reduce line length mismatch to insure added margin. In order to reduce trace to trace coupling

(crosstalk), separate the traces as much as possible. All signals in a signal group should be routed

on the same layer. The trace length and trace spacing requirements must not be violated by any

signal. Trace length mismatch for all signals within a signal group should be as close to zero as

possible to provide timing margin.

Table 26. AGP 2.0 Routing Summary

Signal Maximum

Length

Trace Spacing

(5 mil traces)

Length

Mismatch

Relative To

1X Timing Domain 7.5 inches 5 mils No requirement N/A

2X/4X Timing

Domain Set #1

7.25 inches 20 mils

3

±0.125 inches

2

AD_STB0 and

AD_STB0#

2X/4X Timing

Domain Set #2

7.25 inches 20 mils

3

±0.125 inches

2

AD_STB1 and

AD_STB1#

2X/4X Timing

Domain Set #3

7.25 inches 20 mils

3

±0.125 inches

2

SB_STB and

SB_STB#

2X/4X Timing

Domain Set #1

6 inches 15 mils

1,3

±0.25 inches

2

AD_STB0 and

AD_STB0#

2X/4X Timing

Domain Set #2

6 inches 15 mils

1,3

±0.25 inches

2

AD_STB1 and

AD_STB1#

2X/4X Timing

Domain Set #3

6 inches 15 mils

1,3

±0.25 inches

2

SB_STB and

SB_STB#

2X/4X Timing

Domain Set #1

6 inches 20 mils

1,4

±0.25 inches

2

AD_STB0 and

AD_STB0#

2X/4X Timing

Domain Set #2

6 inches 20 mils

1,4

±0.25 inches

2

AD_STB1 and

AD_STB1#

2X/4X Timing

Domain Set #3

6 inches 20 mils

1,4

±0.25 inches

2

SB_STB and

SB_STB#

NOTES:

1. Each strobe pair must be separated from other signals by at least 20 mils.

2. Each strobe pair must be the same length.

3. These guidelines apply to board stack-ups with 10% impedance tolerance.

4. These guidelines apply to board stack-ups with 15% impedance tolerance

Loading...

Loading...