Intel® Pentium® 4 Processor in the 478-Pin Package Processor Power Distribution Guidelines

R

226 Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide

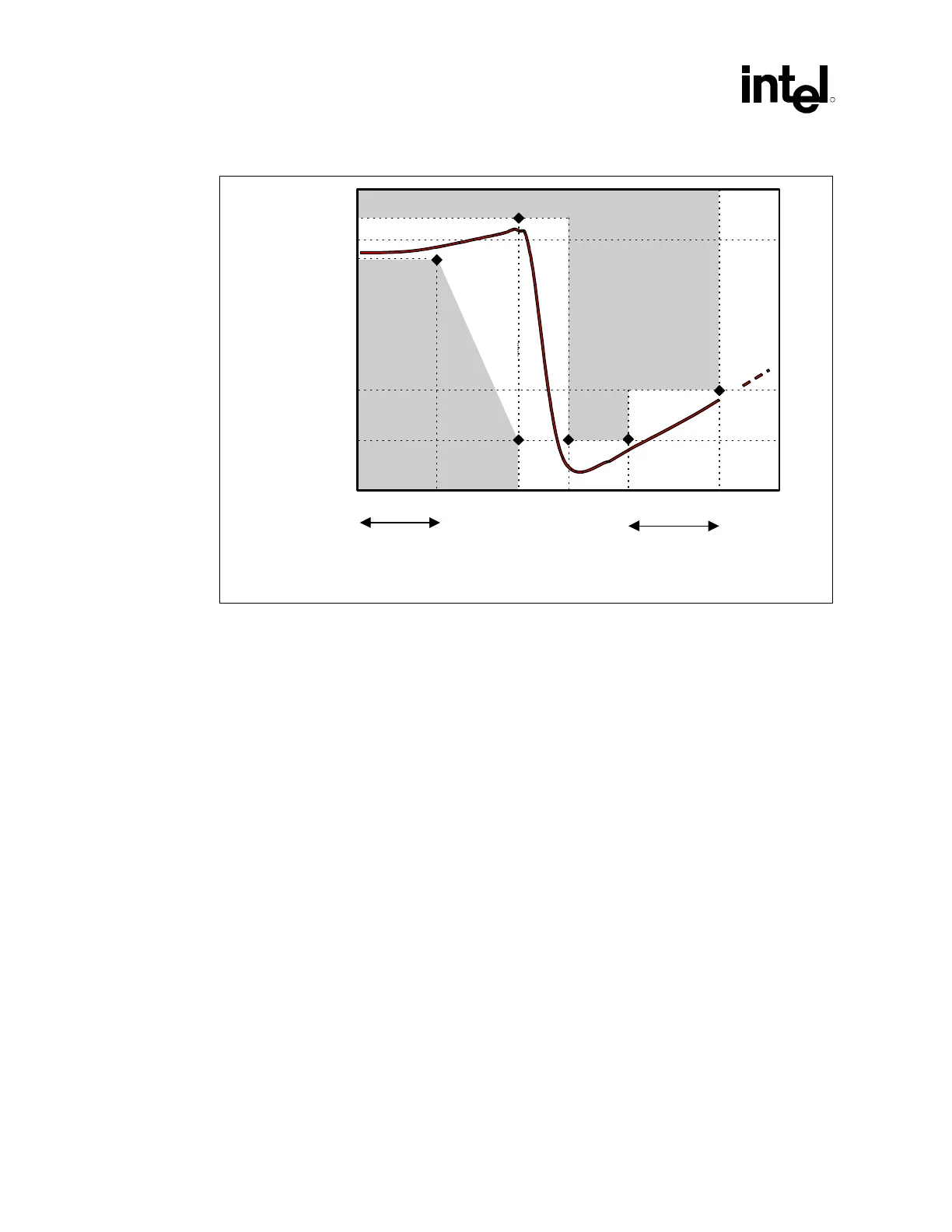

Figure 169. Filter Recommendation

0 dB

-28 dB

-34 dB

0.2 dB

0.5 dB

1 MHz 66 MHz fcorefpeak1 HzDC

passband

high frequency

band

PLL_Filter_Spec

Forbidden

Zone

Forbidden

Zone

NOTES:

1. Diagram not to scale.

2. No specification for frequencies beyond fcore (core frequency).

3. fpeak, if existent, should be less than 0.05 MHz.

Other Recommendations

• Use shielded type inductors to reduce crosstalk

• Capacitors for the filter can be any value between 22 µF and 100 µF as long components with

ESL ≤ 5 nH and ESR < 0.3 Ω are used.

• Values of either 4.7 uH or 10 uH may be used for the inductor. Filter should support

DC current > 60 mA

• DC voltage drop from VCC_CPU to VCCA should be < 60 mV

• In order to maintain a DC drop of less than 60 mV, the total DC resistance of the filter from

VCC_CPU to the processor socket should be a maximum of 1 Ω.

Other Routing Requirements

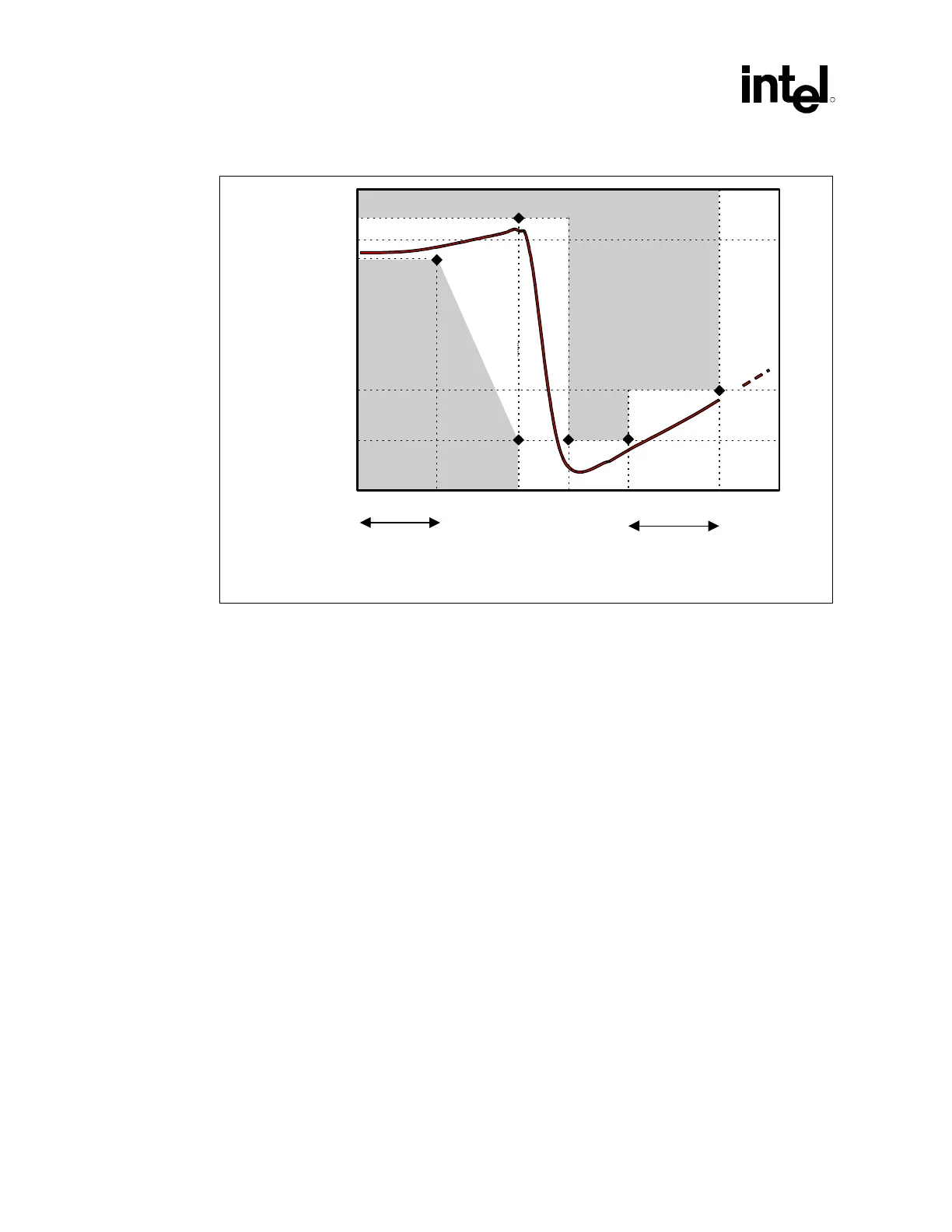

• C should be within 600 mils of the VCCA and VSSA pins. An example of the component

placement is shown in Figure 170.

• VCCA route should be parallel and next to VSSA route (minimize loop area)

• A minimum of a 12 mil trace should be used to route from the filter to the processor pins.

• L should be close to C

Loading...

Loading...