Memory Interface Routing

R

Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide 91

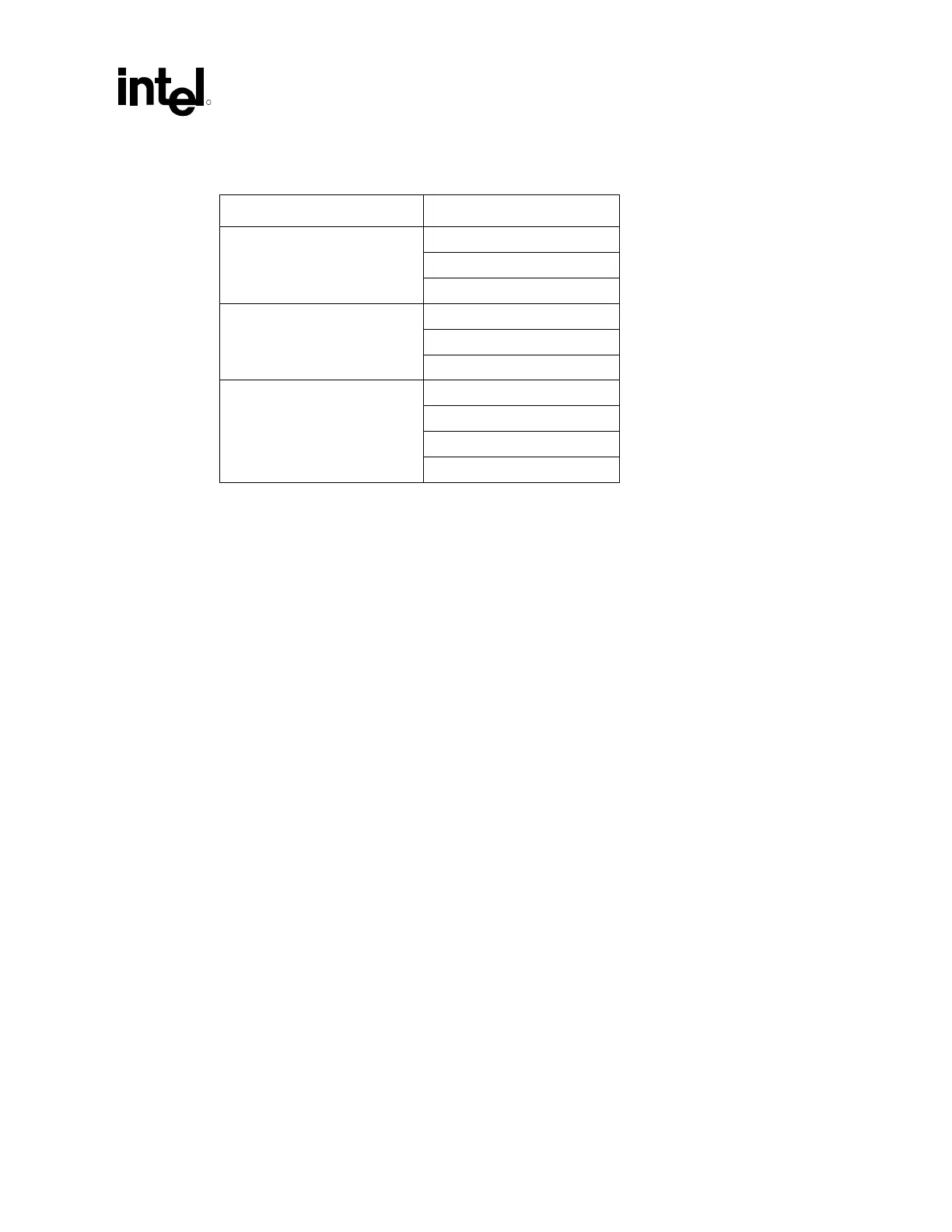

Table 21. Direct Rambus Channel Signal Groups

Group Signal

RSL Signals DQA[8:0]

DQB[8:0]

RQ[7:0]

CMOS Signals CMD

(1)

SCK

*(1)

SIO

Clocking Signals CTM

CTM#

CFM

CFM#

NOTES:

1. These are high-speed CMOS signals

6.1.1 Rambus Signaling Level (RSL) Signals

The Direct Rambus channel RSL signals are high-speed signals that transmit data between the

MCH and RDRAM component at speeds up to 1066 MHz. These signals start at the MCH, enter

the first RIMM connector, propagate through the RIMM module, and then exit on the opposite

side. The RSL signals continue through the second RIMM connector until they are terminated at

V

term

. All unpopulated RIMM connectors must have continuity modules in place to ensure signals

propagate to the termination at the end of the Direct Rambus channel.

Note: For 850E / 533 MHz (PC1066) RDRAM technology platforms, if a continuity module (C-

RIMM) is used, it must be installed in the #2 RIMM slot only – never in the #1 RIMM slot.

The perfect matching of transmission line impedance and uniform trace length are essential for the

Direct RDRAM device interface to work properly. Maintaining 28 Ω ± 10% loaded impedance for

every RSL signal requires some changes to the standard trace width and board prepreg thickness.

Typically, to achieve 28 Ω nominal impedance with 7 mil prepreg, it will require 28 mil wide

traces. 28 mils wide traces are too wide to break out of the rows of RSL signals on the MCH. In

order to reduce the trace width, a thinner pregreg is required. For example, a prepreg thickness of

4.0 to 4.5 mils allows 18 mil wide traces to meet the 28 Ω ± 10% nominal impedance requirement.

Loading...

Loading...