I/O Controller Hub 2

R

164 Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide

9.9.1 Intel

®

ICH2 – LAN Interconnect Guidelines

This section contains guidelines to the design of motherboards and riser cards to comply with LAN

Connect. It should not be treated as a specification and the system designer must ensure through

simulations or other techniques that the system meets the specified timings. Special care must be

given to matching the LAN_CLK traces to those of the other signals, as shown below. The

following are guidelines for the ICH2 to LAN component interface. The following signal lines are

used on this interface:

• LAN_CLK

• LAN_RSTSYNC

• LAN_RXD[2:0]

• LAN_TXD[2:0]

This interface supports both 82562EH and 82562ET/82562EM components. Signal lines

LAN_CLK, LAN_RSTSYNC, LAN_RXD[0], and LAN_TXD[0] are shared by both components.

Signal lines LAN_RXD[2:1] and LAN_TXD[2:1] are not connected when 82562EH is installed

Dual footprint guidelines are described in Section 9.9.6.

9.9.1.1 Bus Topologies

The LAN Connect Interface can be configured in several topologies:

• Direct point-to-point connection between the ICH2 and the LAN component

• Dual Footprint (See Section 9.9.6)

• LOM/CNR Implementation

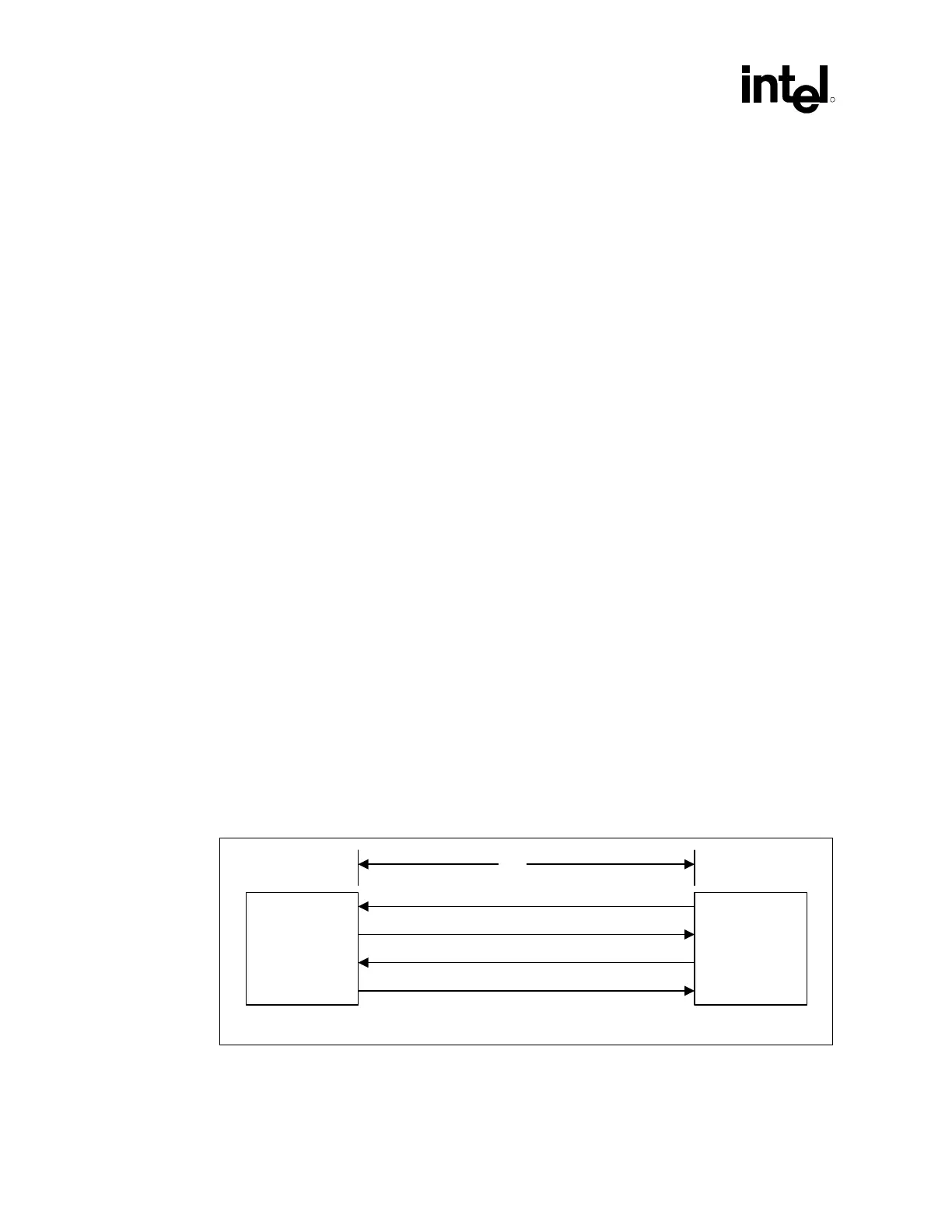

9.9.1.2 Point-to-Point Interconnect

The following are guidelines for a single solution motherboard. Either 82562EH, 82562ET, or

CNR are installed.

Figure 118. Single Solution Interconnect

LAN_single_sol_interconn

ICH2

Platform LAN

Connect

(PLC)

LAN_TXD[2:0]

LAN_RXD[2:0]

LAN_RSTSYNC

LAN_CLK

L

Loading...

Loading...