Hub Interface Routing

R

Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide 127

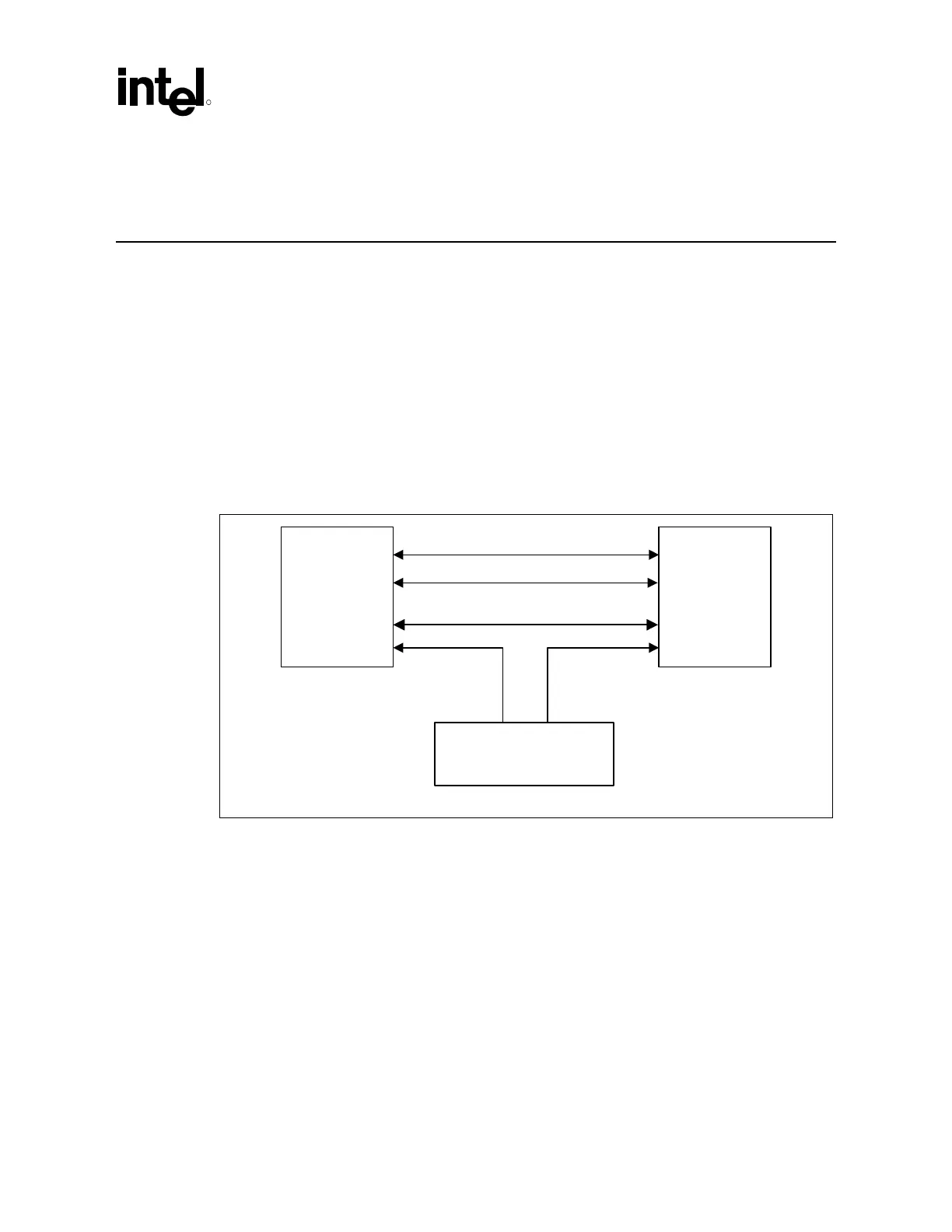

8 Hub Interface Routing

8.1 Hub Interface Routing Guidelines

The MCH and ICH2 ballout assignments have been optimized to simplify the hub interface routing

between these devices. It is recommended that the hub interface signals be routed directly from the

MCH to ICH2 with all signals referenced to VSS. Layer transition should be keep to a minimum.

If a layer change is required, use only two vias per net and keep all data signals and associated

strobe signal on the same layer.

The hub interface signals are broken into two groups: data signals (HL) and strobe signals

(HL_STB). For the 8-bit hub interface, HL[0:7] are associated with HL_STB and HL_STB#.

Figure 83. 8-Bit Hub Interface Routing Example

HL_STB

HL_STB#

HL[11:0]

CLK66

hub_route_8bit

CLK66

Clock

Synthesizer

ICH2 MCH

Loading...

Loading...