I/O Controller Hub 2

R

Intel

®

Pentium

®

4 Processor / Intel

®

850 Chipset Family Platform Design Guide 153

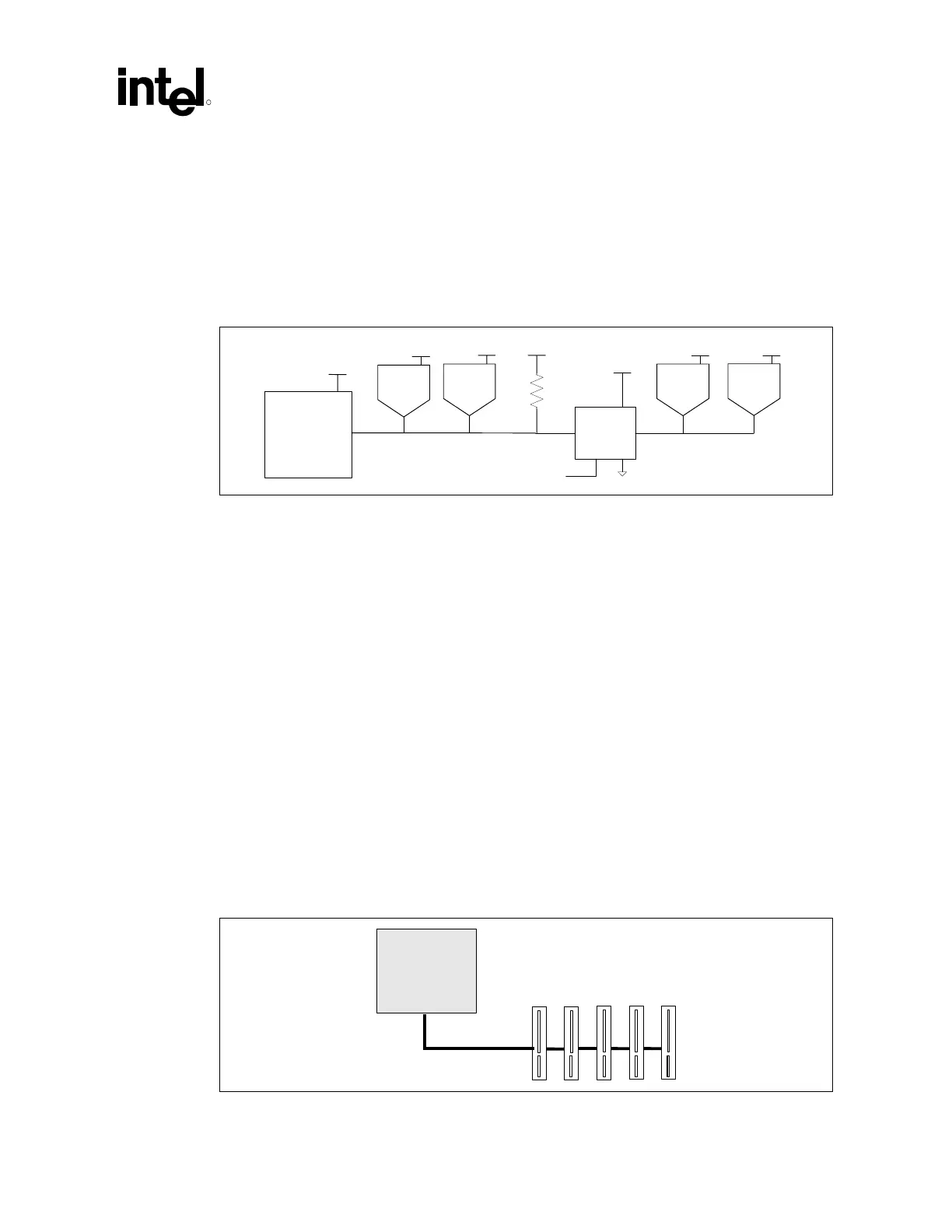

9.6.1.5 Mixed Architecture

This design allows for SMBus devices to communicate while in STR, yet minimizes

VCC_Suspend leakage by keeping non-essential devices on the core supply. This is accomplished

by the use of a “bus switch” to isolate the devices powered by the core and suspend supplies. See

Figure 108.

Figure 108. Mixed VCC_Suspend/VCC_Core Architecture

ICH2

SDRAM

(STR)

Vsus

Vsus Vsus

SM BUS

BUS

SWITCH

OE#

SLP_S3#

CPU

ASIC

Vsus

Vcore

SM BUS

ASICS

RUNNING

IN STR

Vsus

CLKBF

Vcore

Added Considerations for Mixed Architecture:

• The bus switch must be powered by VCC_Suspend

• If there are 5 V SMBus devices used, then an added level translator must be used to separate

those devices driving 5 V from those driving 3 V signal levels.

• Devices that are powered by the VCC_Suspend well must not drive into other devices that are

powered off. This is accomplished with the “bus switch”.

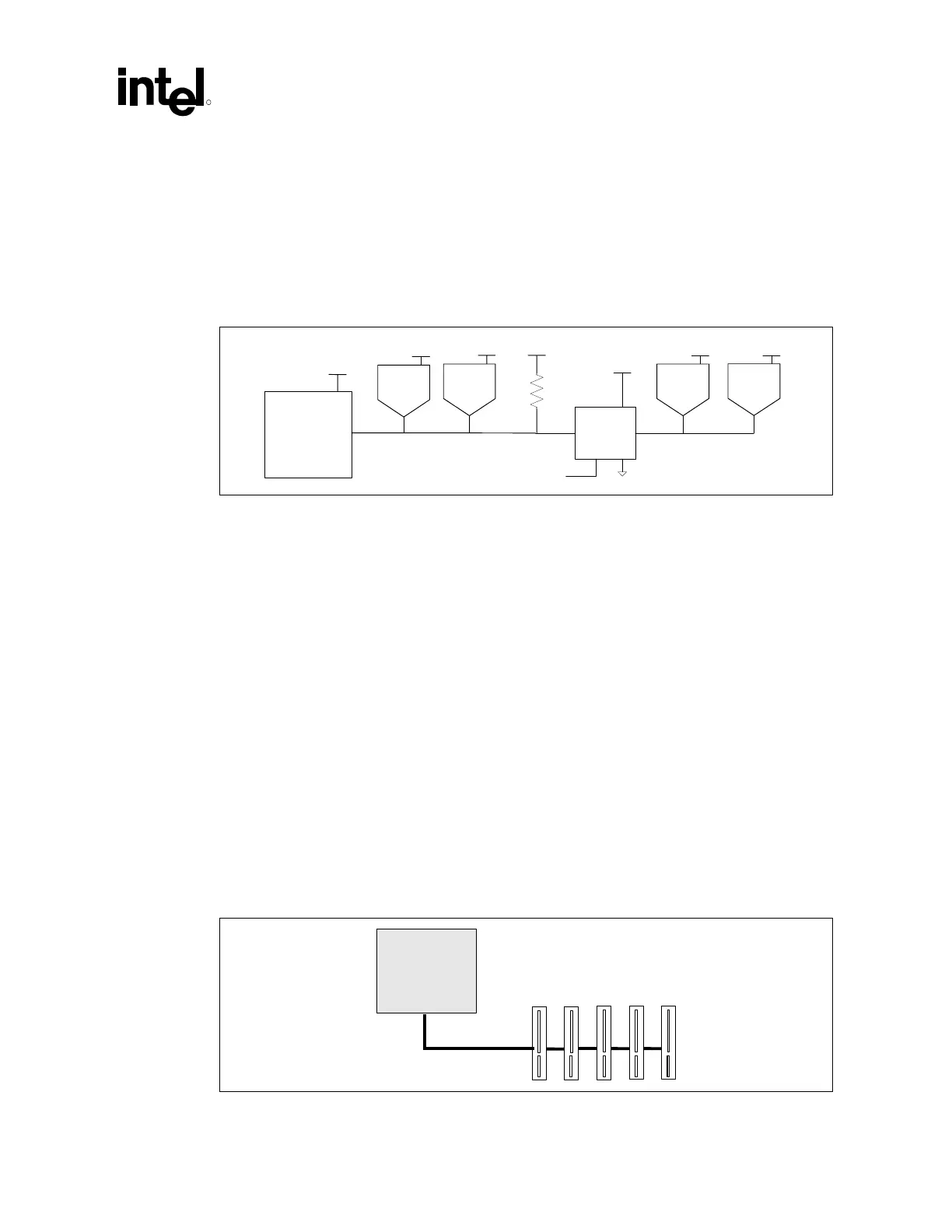

9.7 PCI

The ICH2 provides a PCI Bus interface that is compliant with the PCI Local Bus Specification,

Revision 2.2. The implementation is optimized for high-performance data streaming when the

ICH2 is acting as either the target or the initiator on the PCI bus. For more information on the PCI

Bus interface, refer to the PCI Local Bus Specification, Revision 2.2.

The ICH2 supports six PCI Bus masters (excluding the ICH2), by providing six REQ#/GNT#

pairs. In addition, the ICH2 supports two PC/PCI REQ#/GNT# pairs, one of which is multiplexed

with a PCI REQ#/GNT# pair.

Figure 109. PCI Bus Layout Example

ICH2

Loading...

Loading...