R8C/20 Group, R8C/21 Group 12. Interrupts

Rev.2.00 Aug 27, 2008 Page 90 of 458

REJ09B0250-0200

12.1.5 Interrupts and Interrupt Vector

There are 4 bytes in one vector. Set the starting address of interrupt routine in each vector table. When an

interrupt request is acknowledged, the CPU branches to the address set in the corresponding interrupt vector.

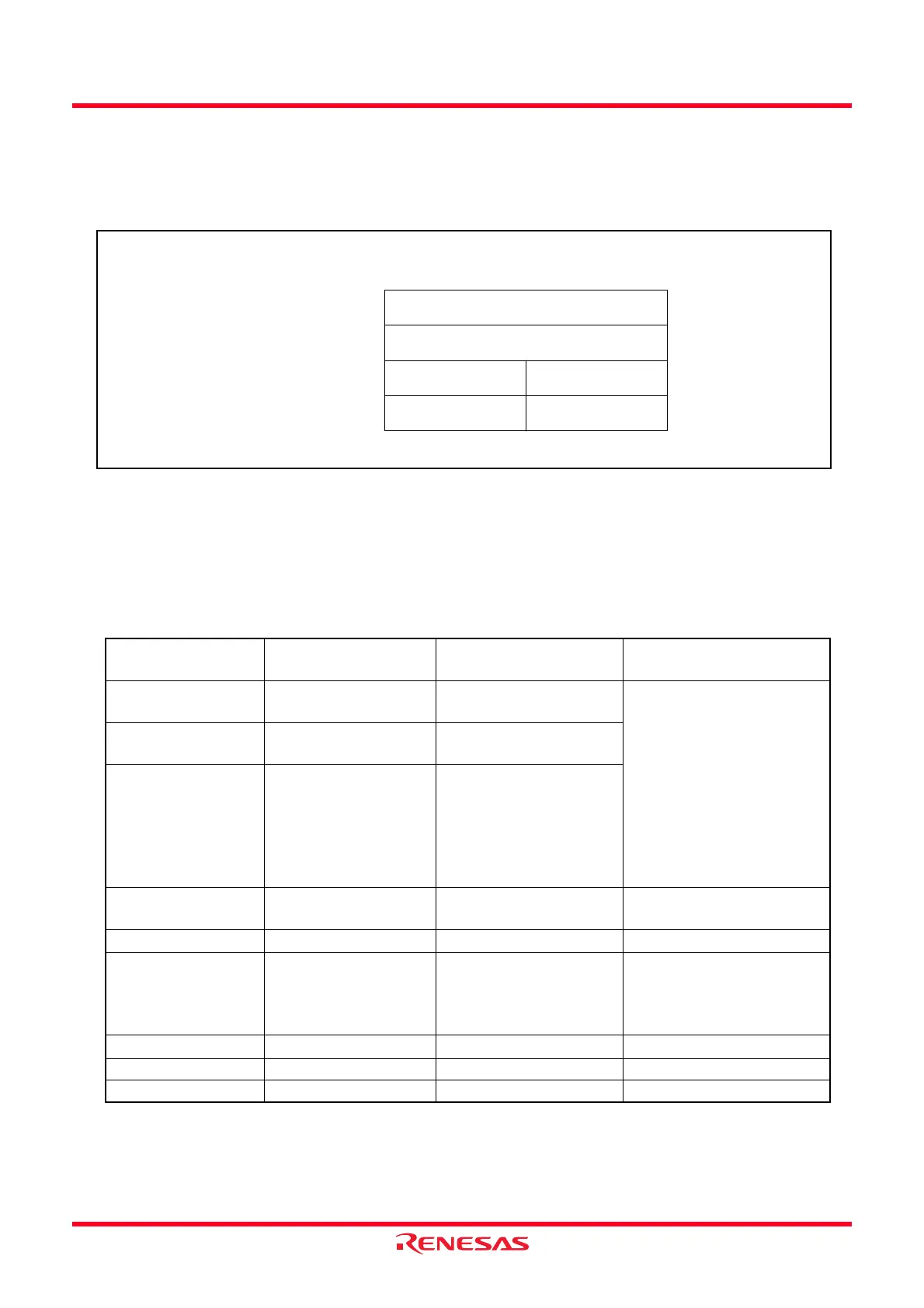

Figure 12.2 shows the Interrupt Vector.

Figure 12.2 Interrupt Vector

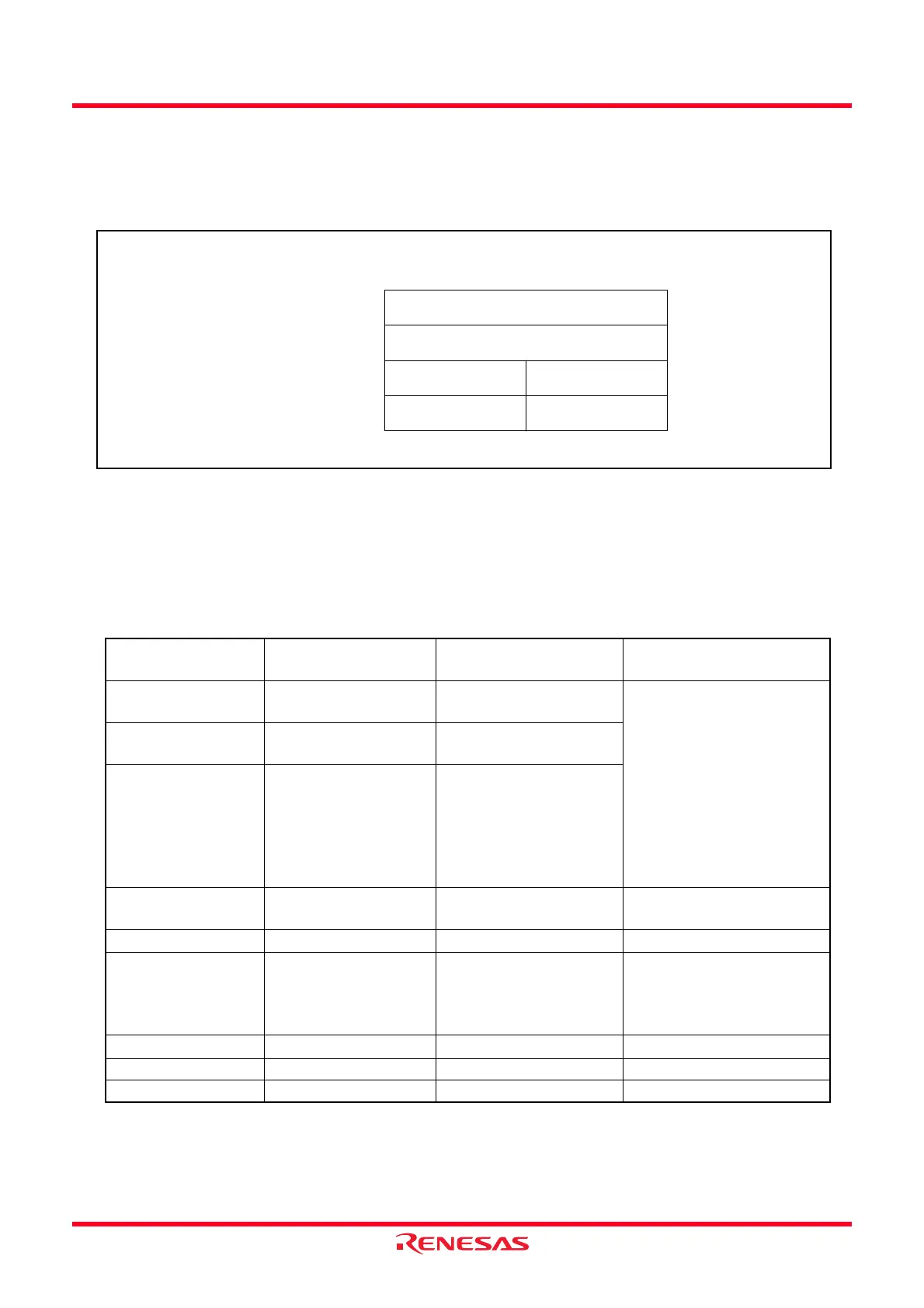

12.1.5.1 Fixed Vector Tables

The fixed vector tables are allocated addresses 0FFDCh to 0FFFFh.

Table 12.1 lists the Fixed Vector Tables. The vector addresses (H) of fixed vectors are used by the ID code

check function. For details, refer to 19.3 Functions to Prevent Rewriting of Flash Memory.

NOTE:

1. Do not use the single-step interrupt. For development tools only.

Table 12.1 Fixed Vector Tables

Interrupt Source

Vector Addresses

Address (L) to (H)

Remarks Reference

Undefined Instruction 0FFDCh to 0FFDFh Interrupt on UND

instruction

R8C/Tiny Series software

manual

Overflow 0FFE0h to 0FFE3h Interrupt on INTO

instruction

BRK Instruction 0FFE4h to 0FFE7h If the content of address

0FFE7h is FFh, program

execution starts from the

address shown by the

vector in the relocatable

vector table.

Address Match 0FFE8h to 0FFEBh 12.4 Address Match

Interrupt

Single Step

(1)

0FFECh to 0FFEFh

Watchdog Timer

Oscillation Stop

Detection

Voltage Monitor 2

0FFF0h to 0FFF3h 13. Watchdog Timer

10. Clock Generation Circuit

6. Voltage Detection Circuit

Address Break

(1)

0FFF4h to 0FFF7h

(Reserved) 0FFF8h to 0FFFBh

Reset 0FFFCh to 0FFFFh 5. Resets

Vector address (L)

Vector address (H)

MSB LSB

Low address

Mid address

High address0 0 0 0

0 0 0 0 0 0 0 0

Loading...

Loading...