R8C/20 Group, R8C/21 Group 18. A/D Converter

Rev.2.00 Aug 27, 2008 Page 360 of 458

REJ09B0250-0200

18. A/D Converter

The A/D converter consists of one 10-bit successive approximation A/D converter circuit with a capacitive coupling

amplifier. The analog input shares the pins with P0_0 to P0_7, P1_0

to P1_3. Therefore, when using these pins, ensure

the corresponding port direction bits are set to 0 (input mode).

When not using the A/D converter, set the VCUT bit in the ADCON1 register to 0 (Vref unconnected), so that no

current will flow from the VREF

pin into the resistor ladder, helping to reduce the power consumption of the chip.

The result of A/D conversion is stored in the AD register.

Table 18.1 lists the Performance of A/D Converter. Figure 18.1 shows the Block Diagram of A/D Converter. Figure

18.2 and Figure 18.3 show the A/D converter-related registers.

NOTES:

1. Analog input voltage does not depend on use of sample and hold function.

When analog input voltage exceeds reference voltage, A/D conversion result is 3FFh in 10-bit

mode, FFh in 8-bit mode.

2. The frequency of φAD must be 10 MHz or below.

Without sample and hold function, the φAD frequency should be 250 kHz or above.

With the sample and hold function, the φAD frequency should be 1 MHz or above.

3. In repeat mode, only 8-bit mode can be used.

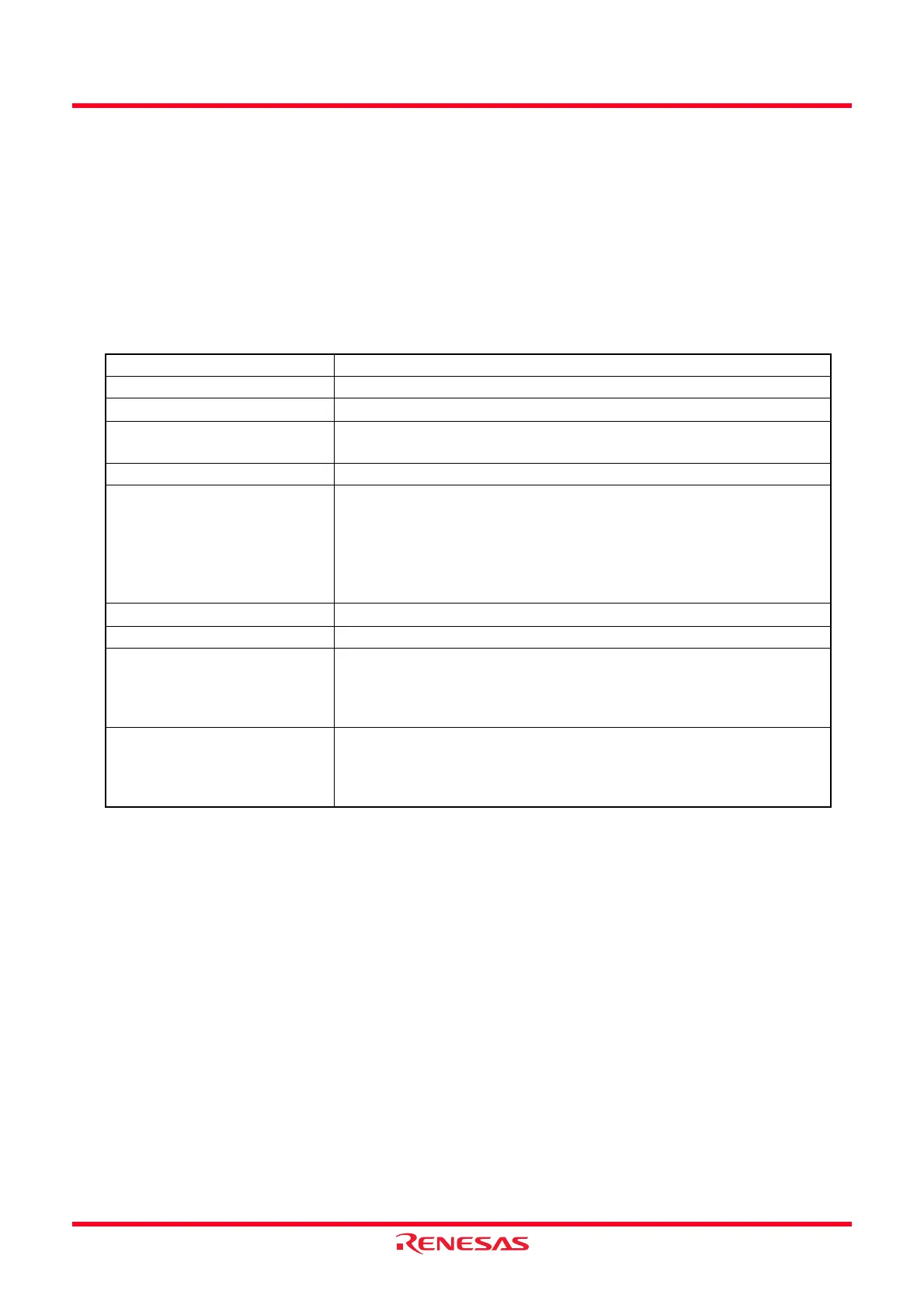

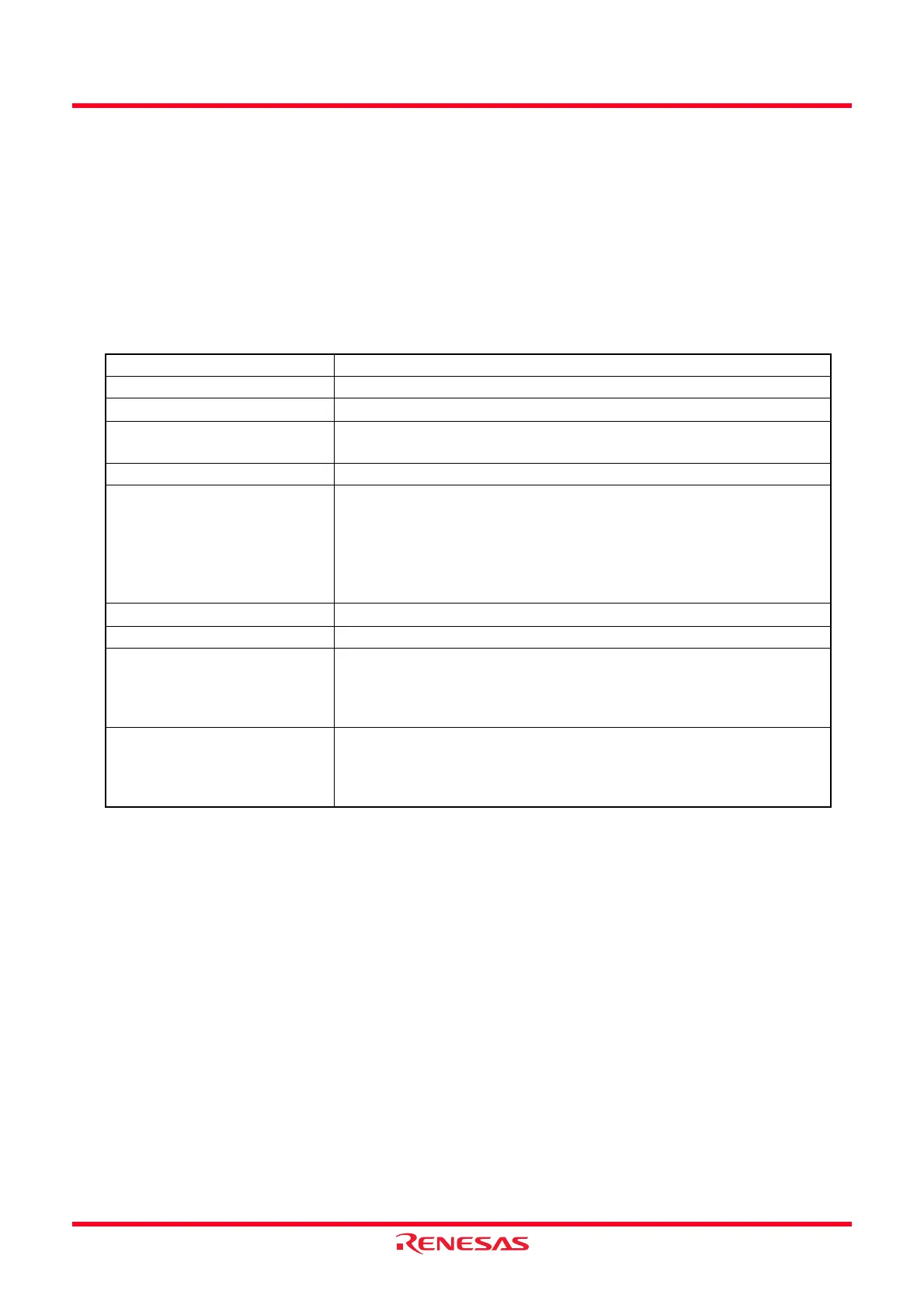

Table 18.1 Performance of A/D Converter

Item Performance

A/D Conversion Method Successive approximation (with capacitive coupling amplifier)

Analog Input Voltage

(1)

0 V to AVCC

Operating Clock φAD

(2)

4.2 V ≤ AVCC ≤ 5.5 V f1, f2, f4, fOCO-F

2.7 V ≤ AVCC < 4.2 V f2, f4, fOCO-F

Resolution 8 bit or 10 bit is selectable

Absolute Accuracy AVCC = Vref = 5 V, φAD = 10MHz

• 8-bit resolution ±2 LSB

• 10-bit resolution ±3 LSB

AVCC = Vref = 3.3 V, φAD = 10MHz

• 8-bit resolution ±2 LSB

• 10-bit resolution ±5 LSB

Operating Mode

One-shot and repeat modes

(3)

Analog Input Pin 12 pins (AN0 to AN11)

A/D Conversion Start Condition • Software trigger

Set the ADST bit in the ADCON0 register to 1 (A/D conversion starts)

•Capture

Timer RD interrupt request is generated while the ADST bit is set to 1

Conversion Rate Per Pin • Without sample and hold function

8-bit resolution: 49φAD cycles, 10-bit resolution: 59φAD cycles

• With sample and hold function

8-bit resolution: 28φAD cycles, 10-bit resolution: 33φAD cycles

Loading...

Loading...