R8C/20 Group, R8C/21 Group 13. Watchdog Timer

Rev.2.00 Aug 27, 2008 Page 116 of 458

REJ09B0250-0200

13.1 Count Source Protection Mode Disabled

The count source of the watchdog timer is the CPU clock when count source protection mode is disabled.

Table 13.2 lists the Watchdog Timer Specifications (with Count Source Protection Mode Disabled).

NOTES:

1. The watchdog timer is reset when writing 00h to the WDTR register before writing FFh. The

prescaler is reset after the MCU is reset. Some errors occur by the prescaler for the period of the

watchdog timer.

2. The WDTON bit cannot be changed by a program. When setting the WDTON bit, write 0 to the bit 0

of the address 0FFFFh using a flash programmer.

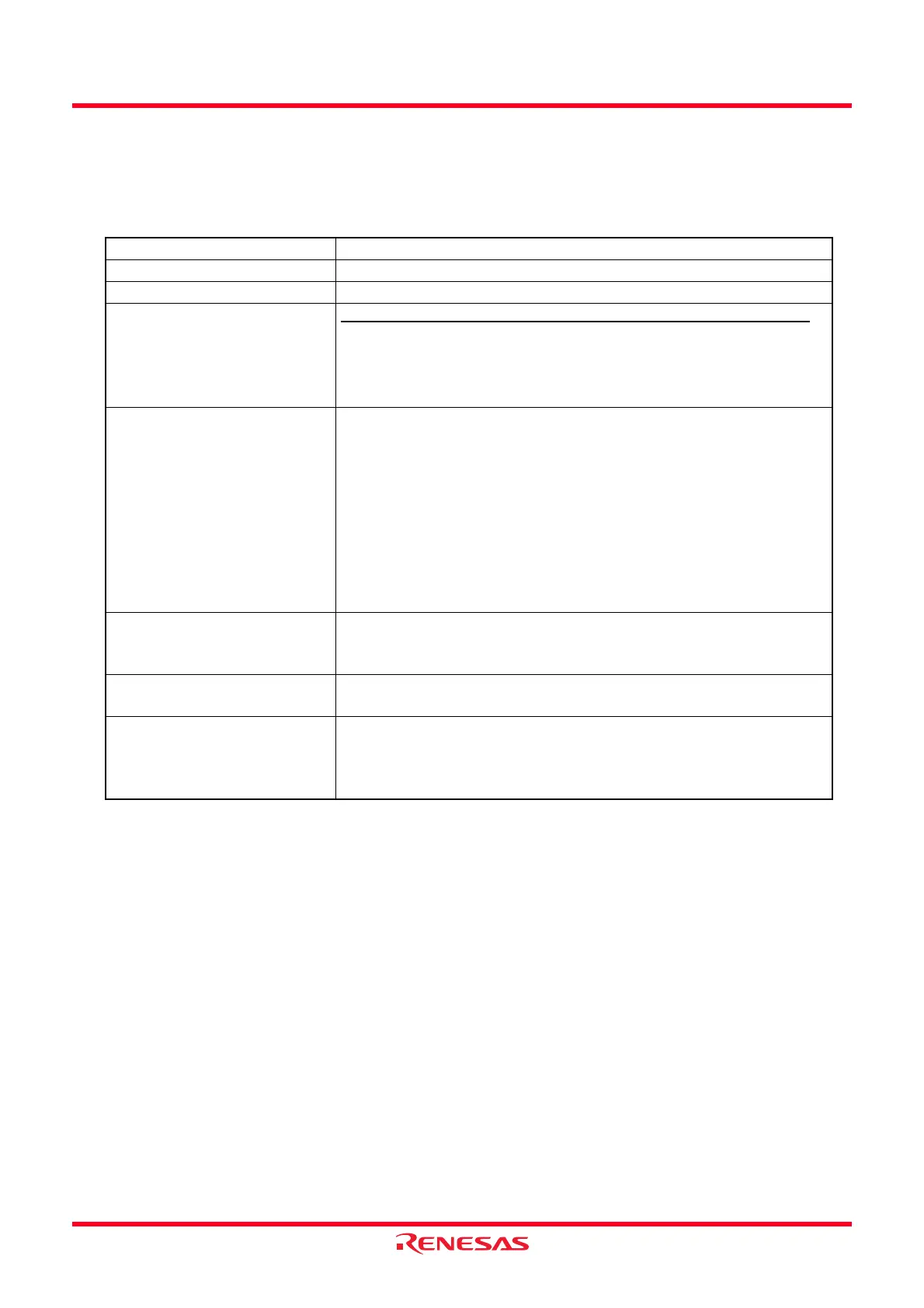

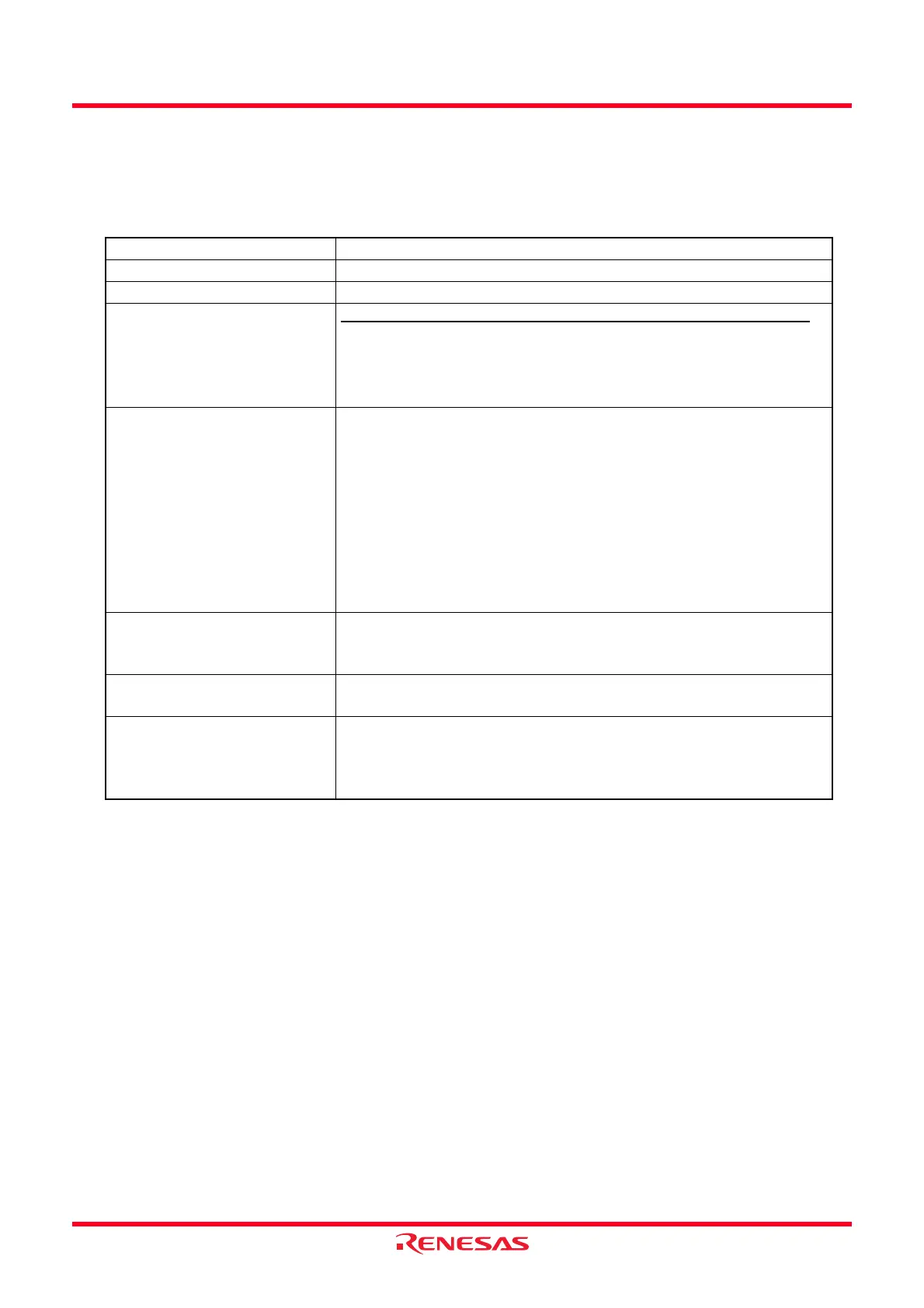

Table 13.2 Watchdog Timer Specifications (with Count Source Protection Mode Disabled)

Item Specification

Count Source CPU clock

Count Operation Decrement

Period

Division ratio of prescaler(n) x count value of watchdog timer(32768)

(1)

CPU clock

n: 16 or 128 (selected by WDC7 bit in WDC register)

e.g.When the CPU clock is 16 MHz and prescaler is divided by 16, the

period is approximately 32.8 ms

Count Start Condition

The WDTON bit

(2)

in the OFS register (0FFFFh) selects the operation

of watchdog timer after reset

• When the WDTON bit is set to 1 (watchdog timer is in stop state after

reset)

The watchdog timer and prescaler stop after reset and the count

starts by writing to the WDTS register

• When the WDTON bit is set to 0 (watchdog timer starts automatically

after exiting)

The watchdog timer and prescaler start counting automatically after

reset

Reset Condition of Watchdog

Timer

• Reset

• Write 00h to the WDTR register before writing FFh

• Underflow

Count Stop Condition Stop and wait modes (inherit the count from the held value after exiting

modes)

Operation at the Time of

Underflow

• When the PM12 bit in the PM1 register is set to 0

Watchdog timer interrupt

• When the PM12 bit in the PM1 register is set to 1

Watchdog timer reset (refer to 5.5 Watchdog Timer Reset)

Loading...

Loading...