R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 322 of 458

REJ09B0250-0200

16.3.1 Transfer Clock

When the MST bit in the ICCR1 register is set to 0, the transfer clock is the external clock input from the SCL

pin. When the MST bit in the ICCR1 register is set to 1, the transfer clock is the internal clock selected by the

CKS0 to CKS3 bits in the ICCR1 register and the transfer clock is output from the SCL pin.

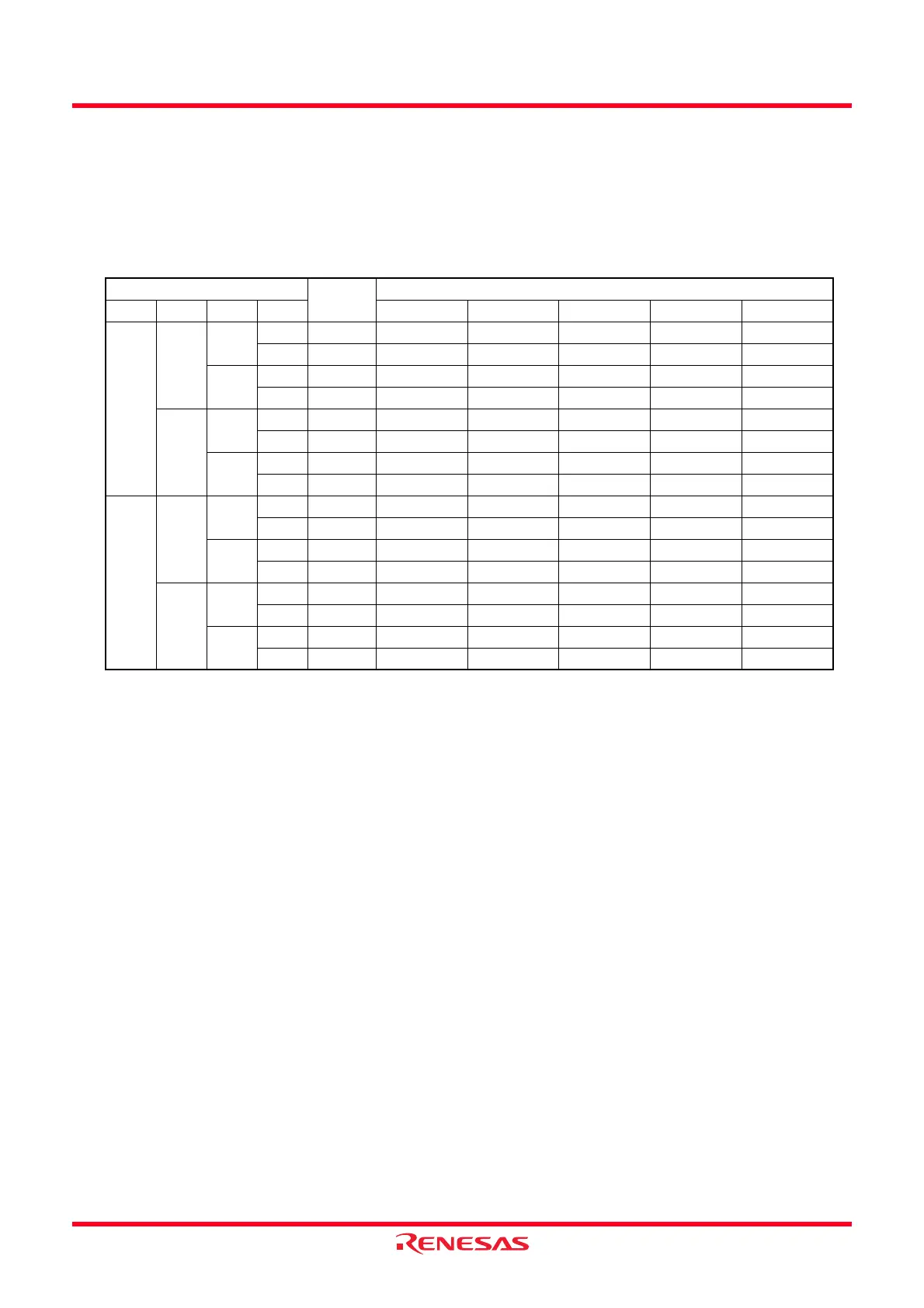

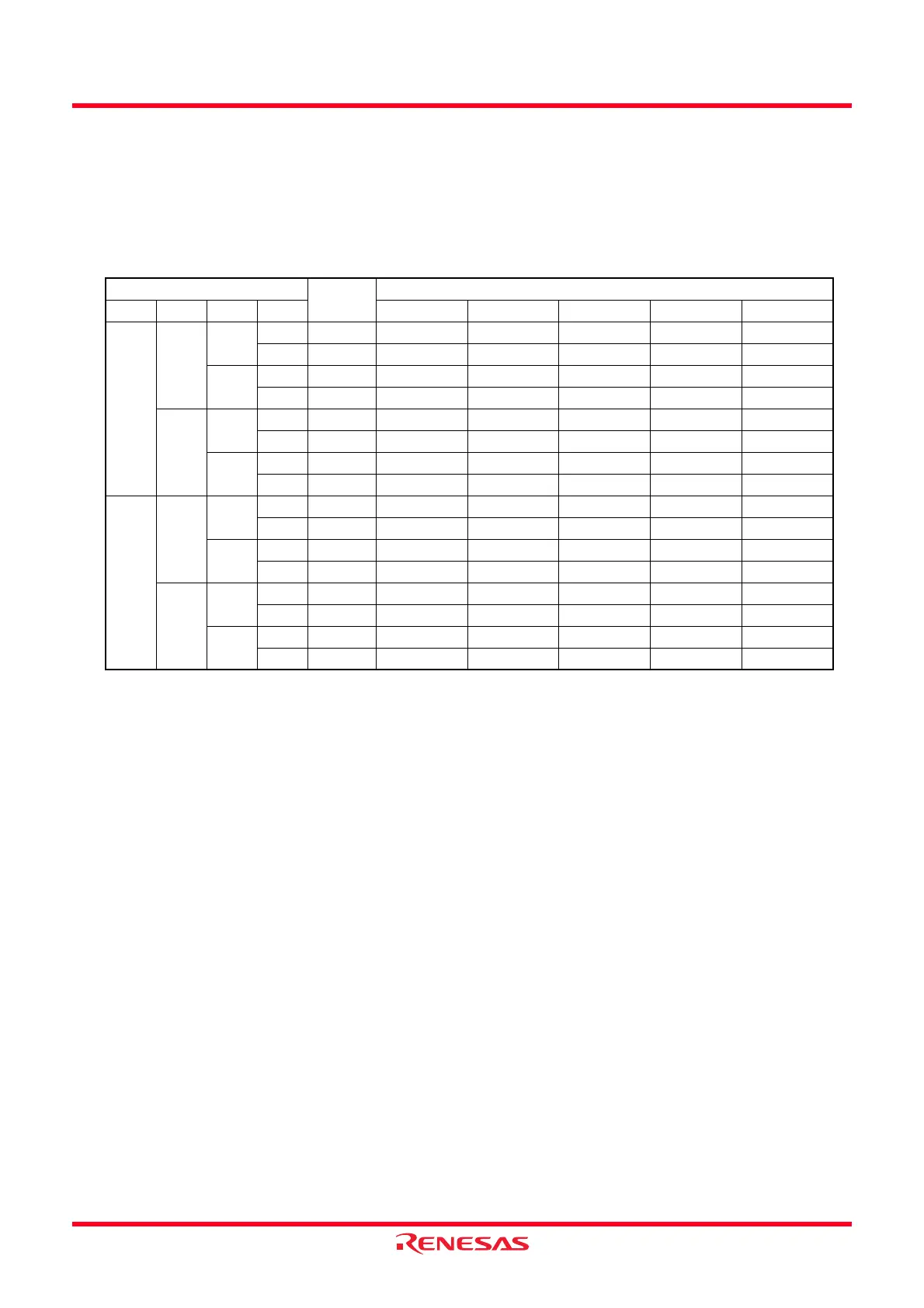

Table 16.6 lists the Transfer Rate Examples.

Table 16.6 Transfer Rate Examples

ICCR1 Register

Transfer

Clock

Transfer Rate

CKS3 CKS2 CKS1 CKS0 f1 = 5 MHz f1 = 8 MHz f1 = 10 MHz f1 = 16 MHz f1 = 20 MHz

0 0 0 0 f1/28 179 kHz 286 kHz 357 kHz 571 kHz 714 kHz

1 f1/40 125 kHz 200 kHz 250 kHz 400 kHz 500 kHz

1 0 f1/48 104 kHz 167 kHz 208 kHz 333 kHz 417 kHz

1 f1/64 78.1 kHz 125 kHz 156 kHz 250 kHz 313 kHz

1 0 0 f1/80 62.5 kHz 100 kHz 125 kHz 200 kHz 250 kHz

1 f1/100 50.0 kHz 80.0 kHz 100 kHz 160 kHz 200 kHz

1 0 f1/112 44.6 kHz 71.4 kHz 89.3 kHz 143 kHz 179 kHz

1 f1/128 39.1 kHz 62.5 kHz 78.1 kHz 125 kHz 156 kHz

1 0 0 0 f1/56 89.3 kHz 143 kHz 179 kHz 286 kHz 357 kHz

1 f1/80 62.5 kHz 100 kHz 125 kHz 200 kHz 250 kHz

1 0 f1/96 52.1 kHz 83.3 kHz 104 kHz 167 kHz 208 kHz

1 f1/128 39.1 kHz 62.5 kHz 78.1 kHz 125 kHz 156 kHz

1 0 0 f1/160 31.3 kHz 50.0 kHz 62.5 kHz 100 kHz 125 kHz

1 f1/200 25.0 kHz 40.0 kHz 50.0 kHz 80.0 kHz 100 kHz

1 0 f1/224 22.3 kHz 35.7 kHz 44.6 kHz 71.4 kHz 89.3 kHz

1 f1/256 19.5 kHz 31.3 kHz 39.1 kHz 62.5 kHz 78.1 kHz

Loading...

Loading...