R8C/20 Group, R8C/21 Group 14. Timers

Rev.2.00 Aug 27, 2008 Page 232 of 458

REJ09B0250-0200

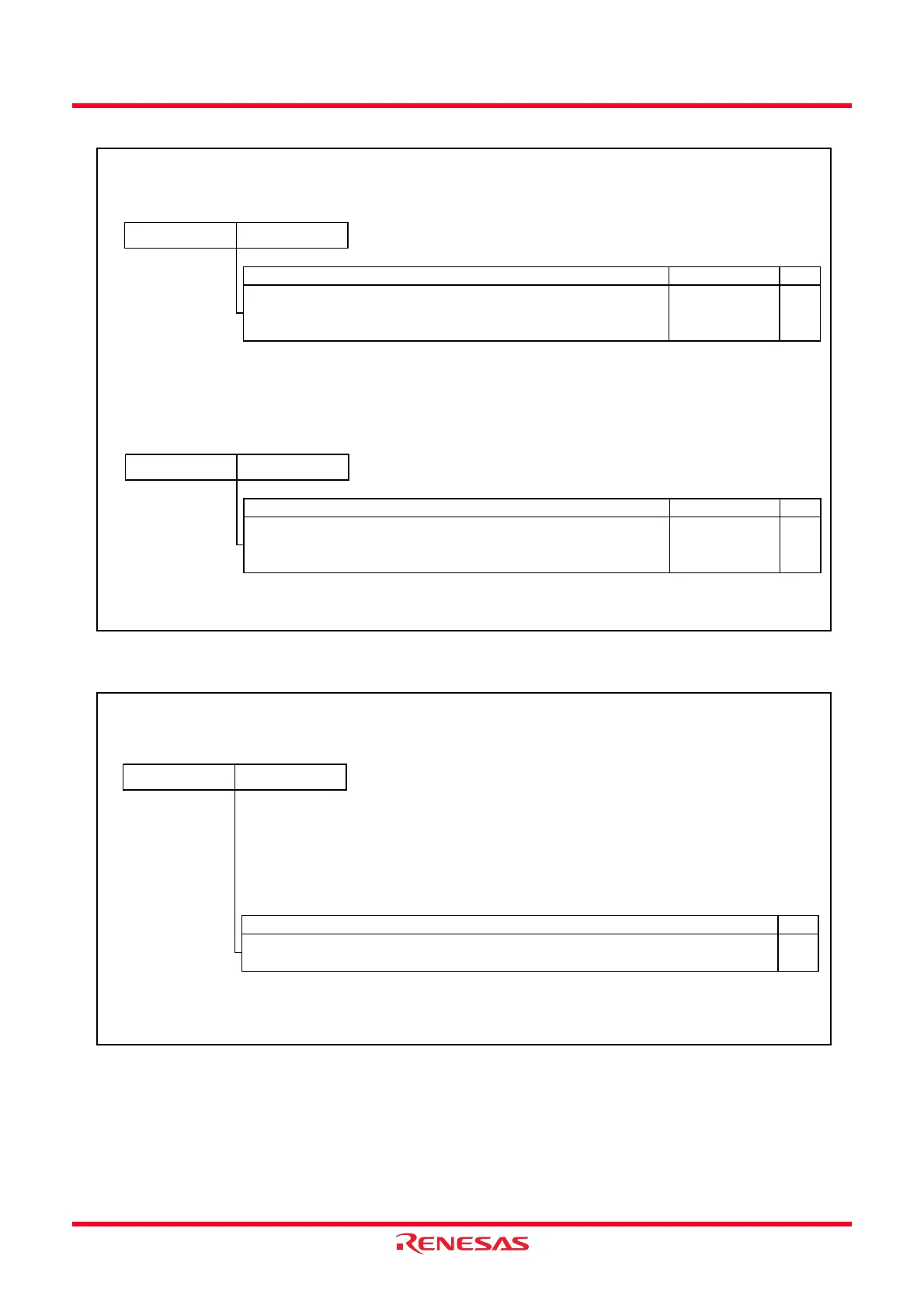

Figure 14.94 Registers TRD0 to TRD1 in Complementary PWM Mode

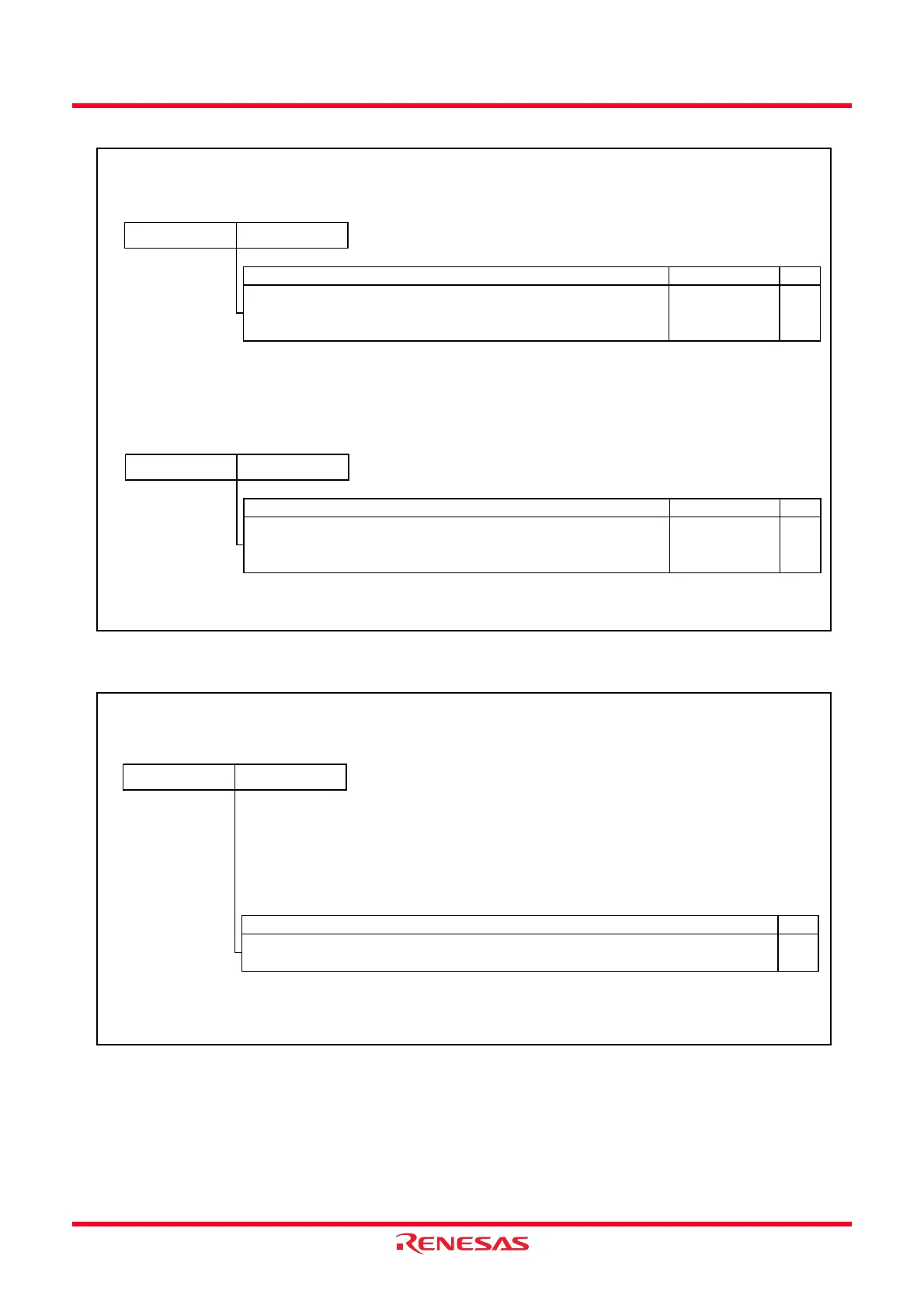

Figure 14.95 Registers TRDGRAi, TRDGRBi, TRDGRC1 and TRDGRDi in Complementary PWM

Mode

The following registers are disabled in the complementary PWM mode:

TRDPMR, TRDOCR, TRDDF0, TRDDF1, TRDIORA0, TRDIORC0, TRDPOCR0, TRDIORA1, TRDIORC1

and TRDPOCR1

Timer RD Counter 0

(1)

Symbol Address After Reset

TRD0

0147h-0146h 0000h

Setting Range RW

NOTE:

1.

Function

Set the dead time.

Count a count source. Count operation is incremented or decremented.

When an overflow occurs, the OVF bit in the TRDSR0 register is set to 1.

0000h to FFFFh RW

Access the TRD0 register in 16-bit units. Do not access it in 8-bit units.

b0b7

(b8)

b0

(b15)

b7

Timer RD Counter 1

(1)

Symbol Address After Reset

TRD1

0157h-0156h 0000h

Setting Range RW

NOTE:

1.

(b8)

b0

(b15)

b7

Access the TRD1 register in 16-bit units. Do not access it in 8-bit units.

b0b7

Function

Select 0000h.

Count a count source. Count operation is incremented or decremented.

When an underflow occurs, the UDF bit in the TRDSR1 register is set to 1.

0000h to FFFFh RW

Timer RD General Register Ai, Bi, C1 and Di (i = 0 or 1)

(1,2)

Symbol Address After Reset

TRDGRA0

TRDGRB0

TRDGRD0

TRDGRA1

TRDGRB1

TRDGRC1

TRDGRD1

0149h-0148h

014Bh-014Ah

014Fh-014Eh

0159h-0158h

015Bh-015Ah

015Dh-015Ch

015Fh-015Eh

FFFFh

FFFFh

FFFFh

FFFFh

FFFFh

FFFFh

FFFFh

RW

NOTES:

1.

2. The TRDGRC0 register is not used in complementary PWM mode.

RW

Function

Ref er to

Table 14.32 TRDGRji Register Functions in Complementary PWM Mode

Access the TRDGRAi to TRDGRDi registers in 16-bit units. Do not access them in 8-bit units.

b0b7

(b8)

b0

(b15)

b7

Loading...

Loading...