R8C/20 Group, R8C/21 Group 15. Serial Interface

Rev.2.00 Aug 27, 2008 Page 269 of 458

REJ09B0250-0200

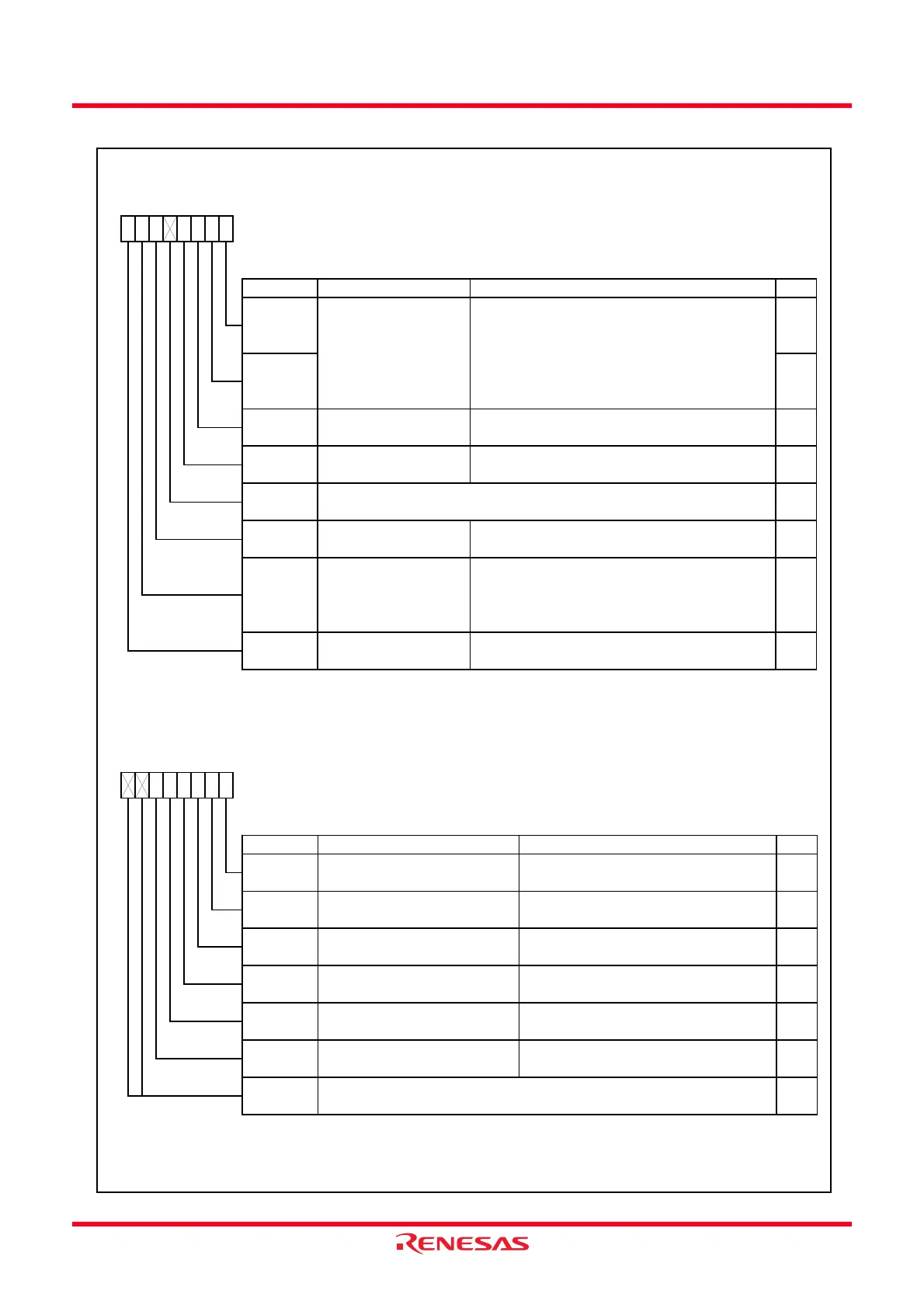

Figure 15.5 Registers UiC0 and UiC1 (i = 0 or 1)

UARTi Transmit/Receive Control Register 0 (i = 0 or 1)

Symbol Address After Reset

U0C0

00A4h 00001000b

U1C0

00ACh 00001000b

Bit Symbol Bit Name Function RW

NOTE:

1.

RW

RW

If the BRG count source is sw itched, set the UiBRG register again.

RW

Data output select bit 0 : TXDi pin is a pin of CMOS output

1 : TXDi pin is a pin of N-channel open drain output

UFORM

Transfer format select bit 0 : LSB first

1 : MSB first

NCH

CLK polarity select bit 0 : Transmit data is output at falling edge of transfer

clock and receive data is input at rising edge

1 : Transmit data is output at rising edge of transfer

clock and receive data is input at falling edge

Set to 0

Transmit register empty

flag

0 : Data in transmit register (during transmit)

1 : No data in transmit register (transmit completed)

Nothing is assigned. If necessary, set to 0.

When read, the content is 0.

—

(b2)

CKPOL

CLK1 RW

BRG count source select

bit

(1)

b1 b0

0 0 : Selects f1

0 1 : Selects f8

1 0 : Selects f32

1 1 : Do not set

RW

RW

RO

—

(b4)

—

Reserved bit

b7 b6 b5 b4 b3 b2

TXEPT

b1 b0

0

CLK0

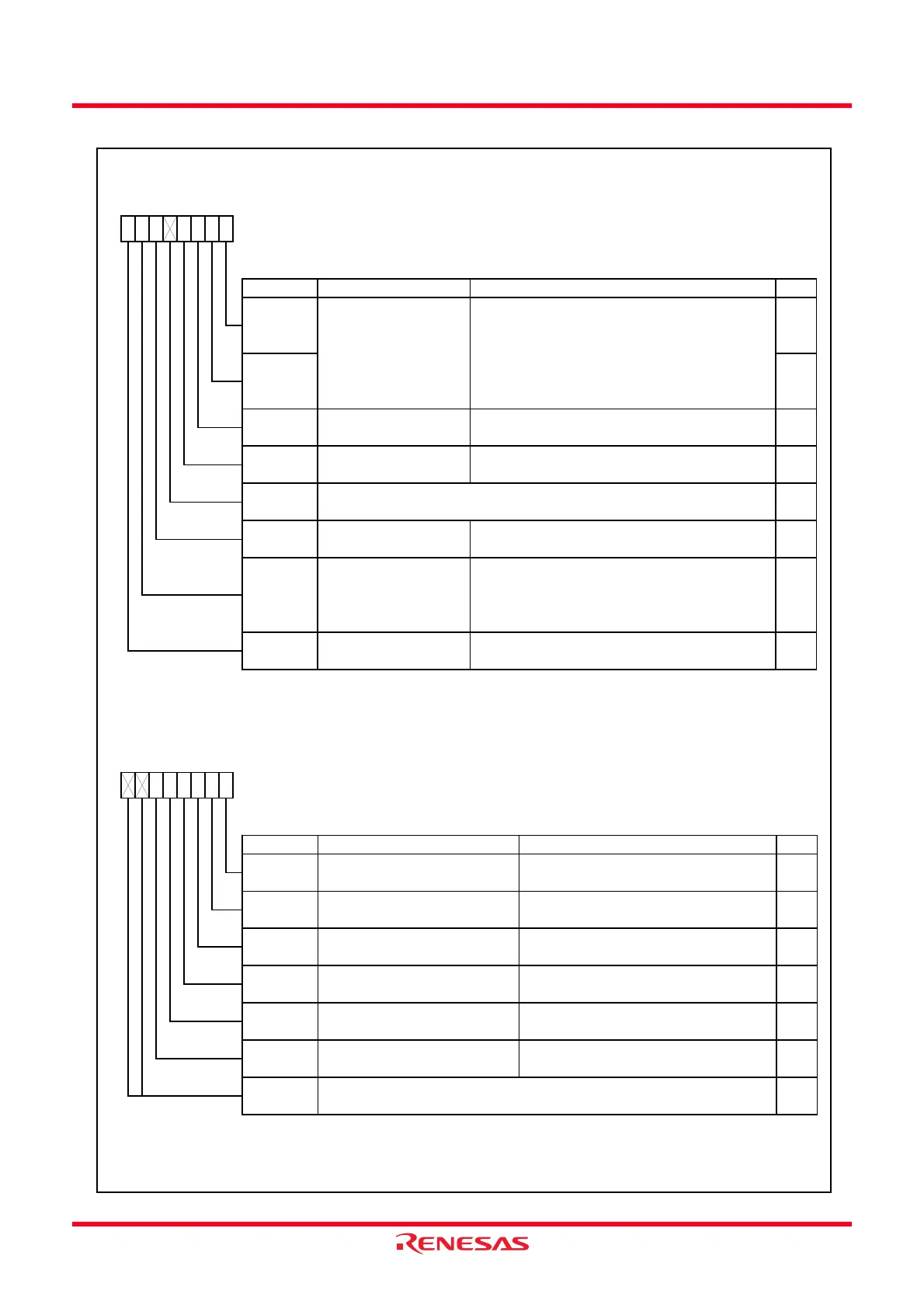

UARTi Transmit/Receive Control Register 1 (i = 0 or 1)

Symbol Address After Reset

U0C1 00A5h 00000010b

U1C1 00ADh 00000010b

Bit Symbol Bit Name Function RW

NOTES:

1.

2. Set the UiRRM bit to 0 (disables continuous receive mode) in UART mode.

RW

RW

UiRRM

UARTi continuous receive mode

enable bit

(2)

RI

Receive complete flag

(1)

0 : No data in UiRB register

1 : Data in UiRB register

RO

UiIRS

The RI bit is set to 0 w hen the higher byte of the UiRB register is read out.

RW

TI RO

0 : Data in UiTB register

1 : No data in UiTB register

TE

RE

—

(b7-b6)

—

b7 b6 b5 b4

Nothing is assigned. If necessary, set to 0.

When read, the content is 0.

Transmit enable bit 0 : Disables transmit

1 : Enables transmit

Transmit buffer empty flag

0 : Disables receive

1 : Enables receive

0 : Disables continuous receive mode

1 : Enables continuous receive mode

0 : Transmit buffer empty (TI = 1)

1 : Transmit completed (TXEPT = 1)

Receive enable bit

RW

b3 b2 b1 b0

UARTi transmit interrupt cause

select bit

Loading...

Loading...