R8C/20 Group, R8C/21 Group 21. Usage Notes

Rev.2.00 Aug 27, 2008 Page 434 of 458

REJ09B0250-0200

21.3.2.2 Programmable waveform generation mode

The following three workarounds should be performed in programmable waveform generation mode.

(1) To write to registers TRBPRE and TRBPR during count operation (TCSTF bit is set to 1), note the

following points:

• When the TRBPRE register is written continuously, allow three or more cycles of the count source for each

write interval.

• When the TRBPR register is written continuously, allow three or more cycles of the prescaler underflow

for each write interval.

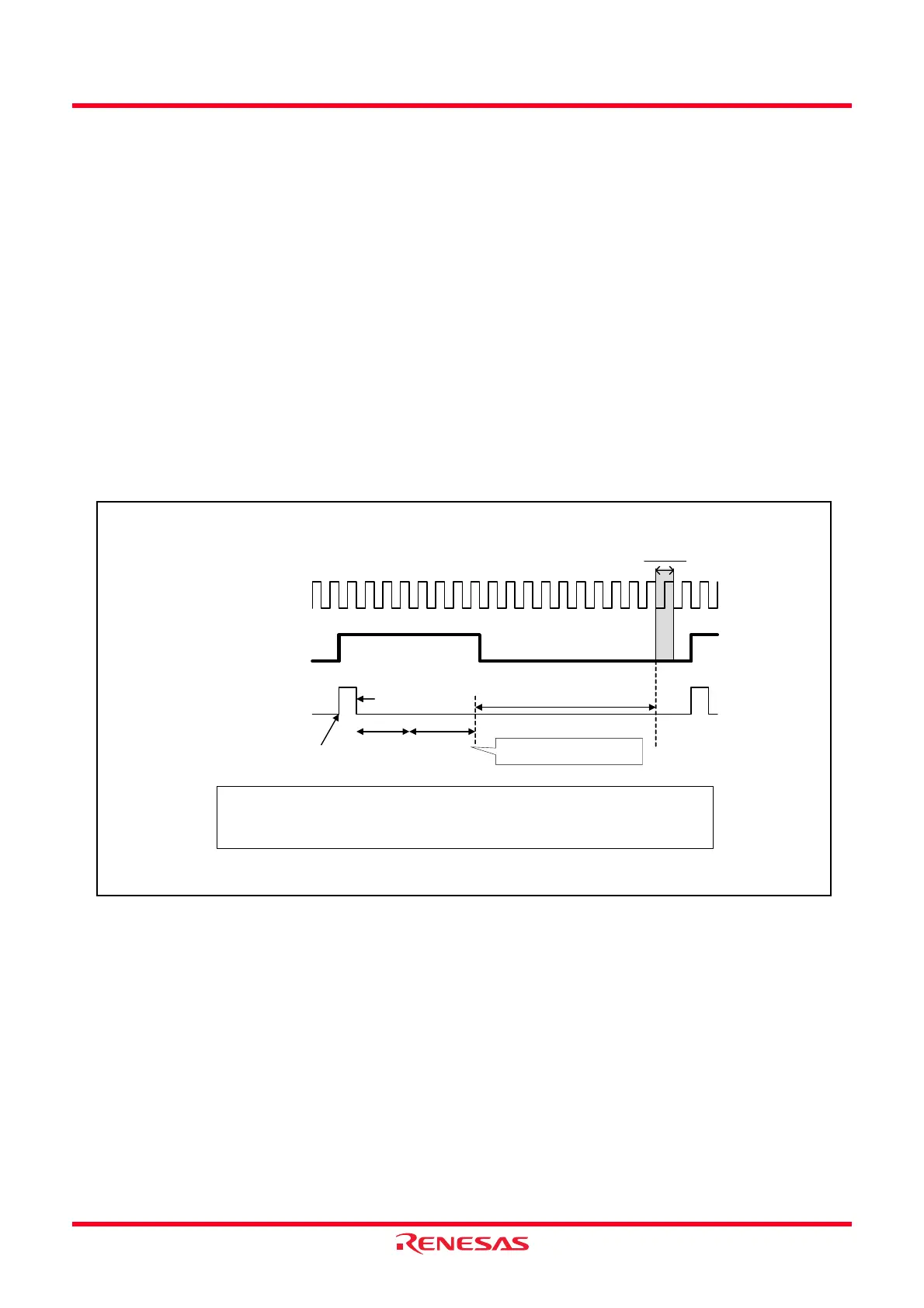

(2) To change registers TRBPRE and TRBPR during count operation (TCSTF bit is set to 1), synchronize

the TRBO output cycle using a timer RB interrupt, etc. This operation should be preformed only once in

the same output cycle. Also, make sure that writing to the TRBPR register does not occur during period

A shown in Figures 21.2 and 21.3.

The following shows the detailed workaround examples.

• Workaround example (a):

As shown in Figure 21.2, write to registers TRBSC and TRBPR in the timer RB interrupt routine. These

write operations must be completed by the beginning of period A.

Figure 21.2 Workaround Example (a) When Timer RB Interrupt is Used

TRBO pin output

Count source/

prescaler

underflow signal

Primary period

Period A

IR bit in

TRBIC register

Secondary period

(b)

Interrupt

sequence

Instruction in

interrupt routine

Interrupt request is

acknowledged

(a)

Interrupt request

is generated

Ensure sufficient time

Set the secondary and then

the primary register immediately

(a) Period between interrupt request generation and the completion of execution of an instruction. The length of time

varies depending on the instruction being executed.

The DIVX instruction requires the longest time, 30 cycles (assuming no wait states and that a register is set as

the divisor).

(b) 20 cycles. 21 cycles for address match and single-step interrupts.

Loading...

Loading...