R8C/20 Group, R8C/21 Group 10. Clock Generation Circuit

Rev.2.00 Aug 27, 2008 Page 65 of 458

REJ09B0250-0200

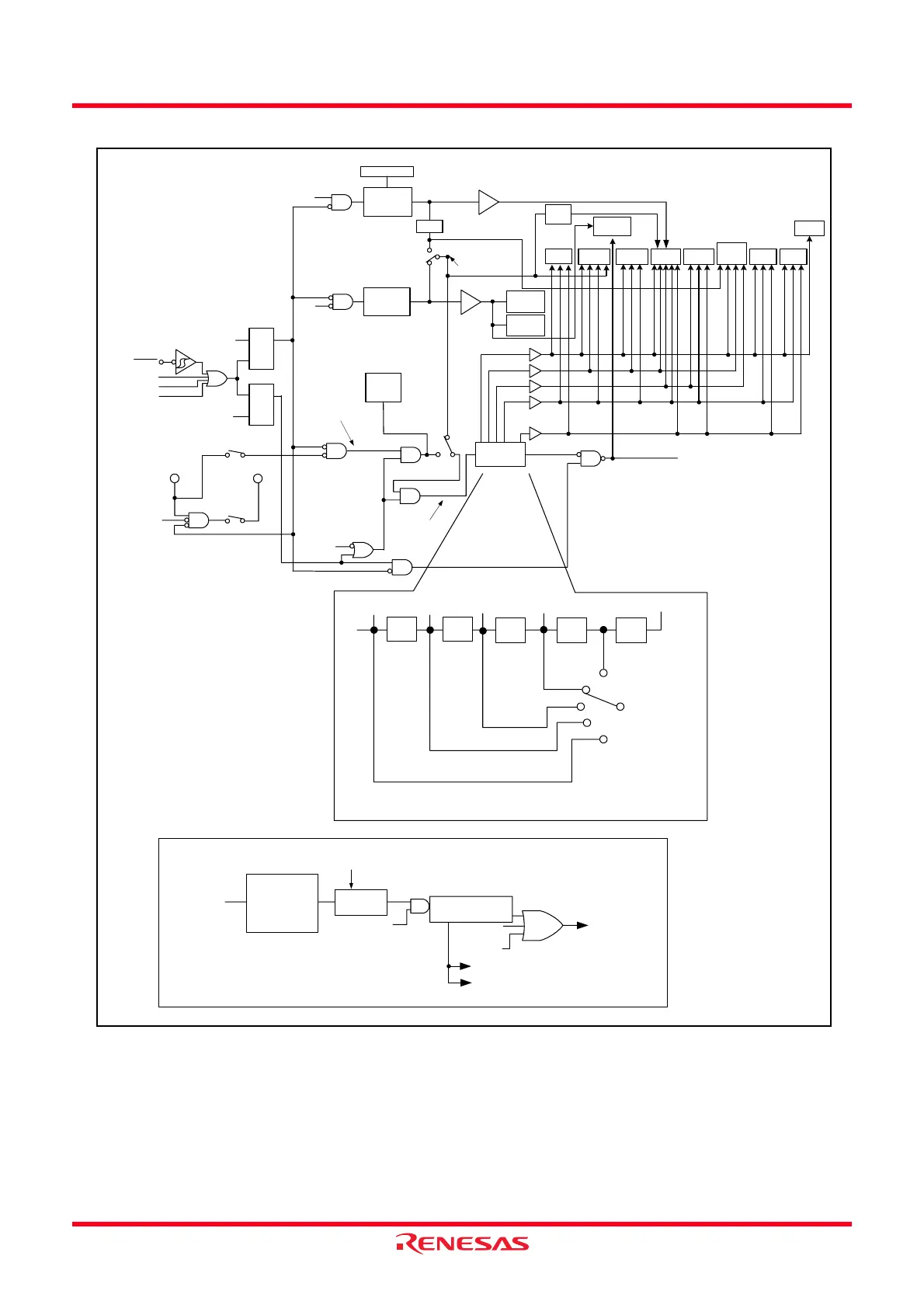

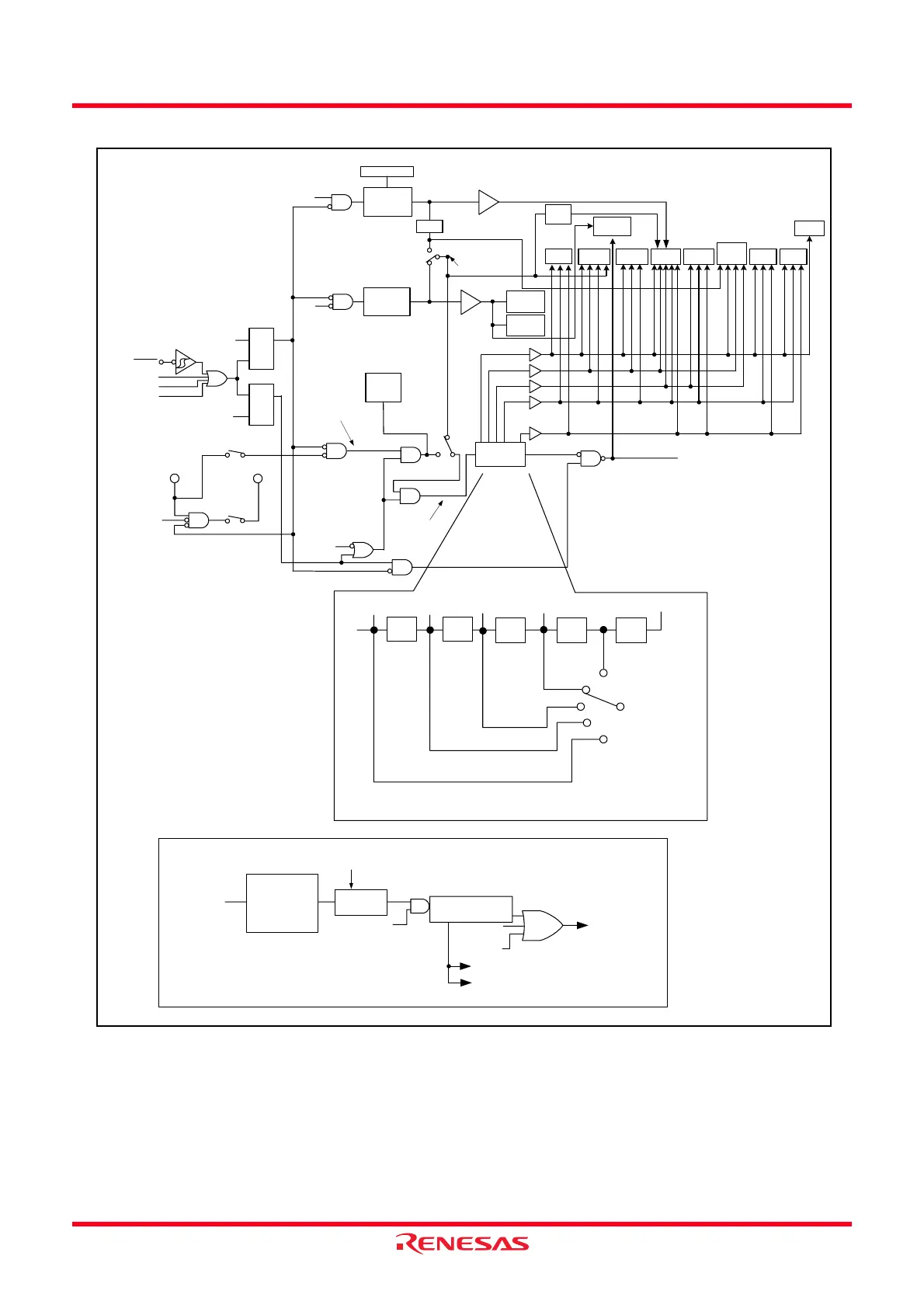

Figure 10.1 Clock Generation Circuit

a

b

c

d

e

g

f1

f2

f4

f8

f32

h

S

Q

R

1/2 1/2

1/2 1/2 1/2

S

Q

R

FRA00

FRA01 = 1

FRA01 = 0

CM14

Power-on

reset

CPU clock

OCD2 = 0

OCD2 = 1

Divider

Oscillation

stop

detection

XIN clock

XOUT

CM13

CM05

XIN

CM02

WAIT

instruction

CM10 = 1 (stop mode)

a

d

c

h

b

CM06 = 0

CM17 to CM16 = 11b

CM06 = 1

CM06 = 0

CM17 to CM16 = 10b

CM06 = 0

CM17 to CM16 = 01b

CM06 = 0

CM17 to CM16 = 00b

Details of divider

Oscillation stop detection circuit

Pulse generation

circuit for clock edge

detection and

charge, discharge

control circuit

XIN clock

Forcible discharge when OCD0 = 0

Charge,

discharge

circuit

Oscillation stop detection

interrupt generation

circuit detection

Watchdog

timer interrupt

OCD1

OCD2 bit switch signal

CM14 bit switch signal

Oscillation stop

detection,

watchdog timer, voltage

monitor 2 interrupt

CM02, CM05, CM06: Bits in CM0 register

CM10, CM13, CM14, CM16, CM17: Bits in CM1 register

OCD0, OCD1, OCD2: Bits in OCD register

FRA00, FRA01: Bits in FRA0 register

e

g

UART0

A/D

converter

Timer RDTimer RBTimer RA

FRA2 register

fOCO

fOCO-S

INT0

SSU/IIC

Voltage watch

2 interrupt

Watchdog

timer

System clock

Low-speed

on-chip

oscillator

FRA1 register

Frequency adjustable

CM13

UART1

Divider

fOCO40M

On-chip oscillator

clock

Timer RE

High-speed

on-chip

oscillator

fOCO-F

Divider

(1/128)

fOCO128

Voltage

detection

circuit

RESET

Power-on reset

Software reset

Interrupt request

Loading...

Loading...