R8C/20 Group, R8C/21 Group 10. Clock Generation Circuit

Rev.2.00 Aug 27, 2008 Page 77 of 458

REJ09B0250-0200

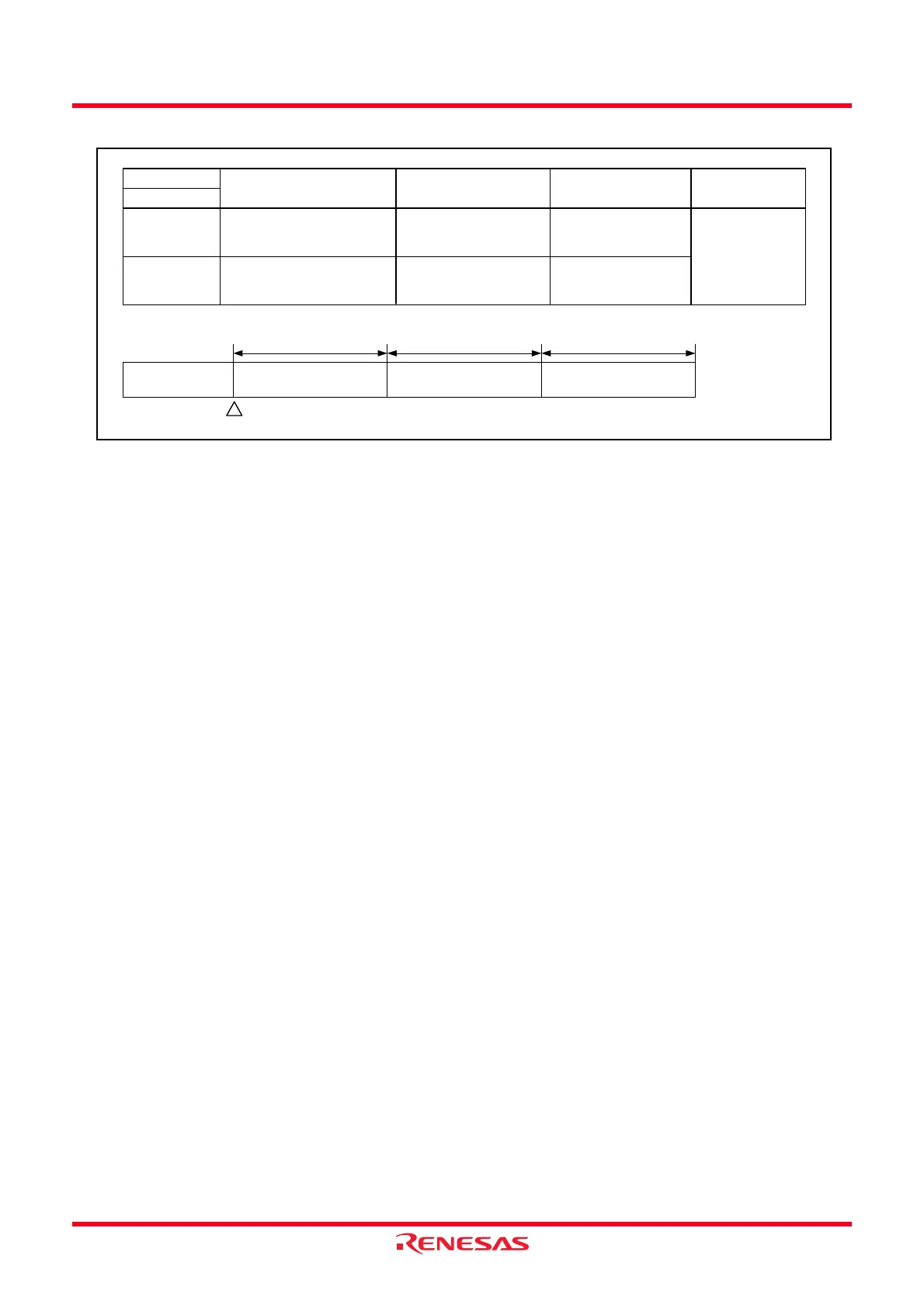

Figure 10.9 Time from Wait Mode to Interrupt Routine Execution

FMR0 Register

FMSTP Bit

Time until Flash Memory is

Activated (T1)

Time until CPU Clock is

Supplied (T2)

Time for Interrupt

Sequence (T3)

Remarks

0

(flash memory

operates)

Period of system clock

× 12 cycles + 30 µs (max.)

Period of CPU clock

× 6 cycles

Period of CPU clock

× 20 cycles

Following total

time is the time

from wait mode

until an interrupt

routine is

executed.

1

(flash memory

stops)

Period of system clock

× 12 cycles

Same as above Same as above

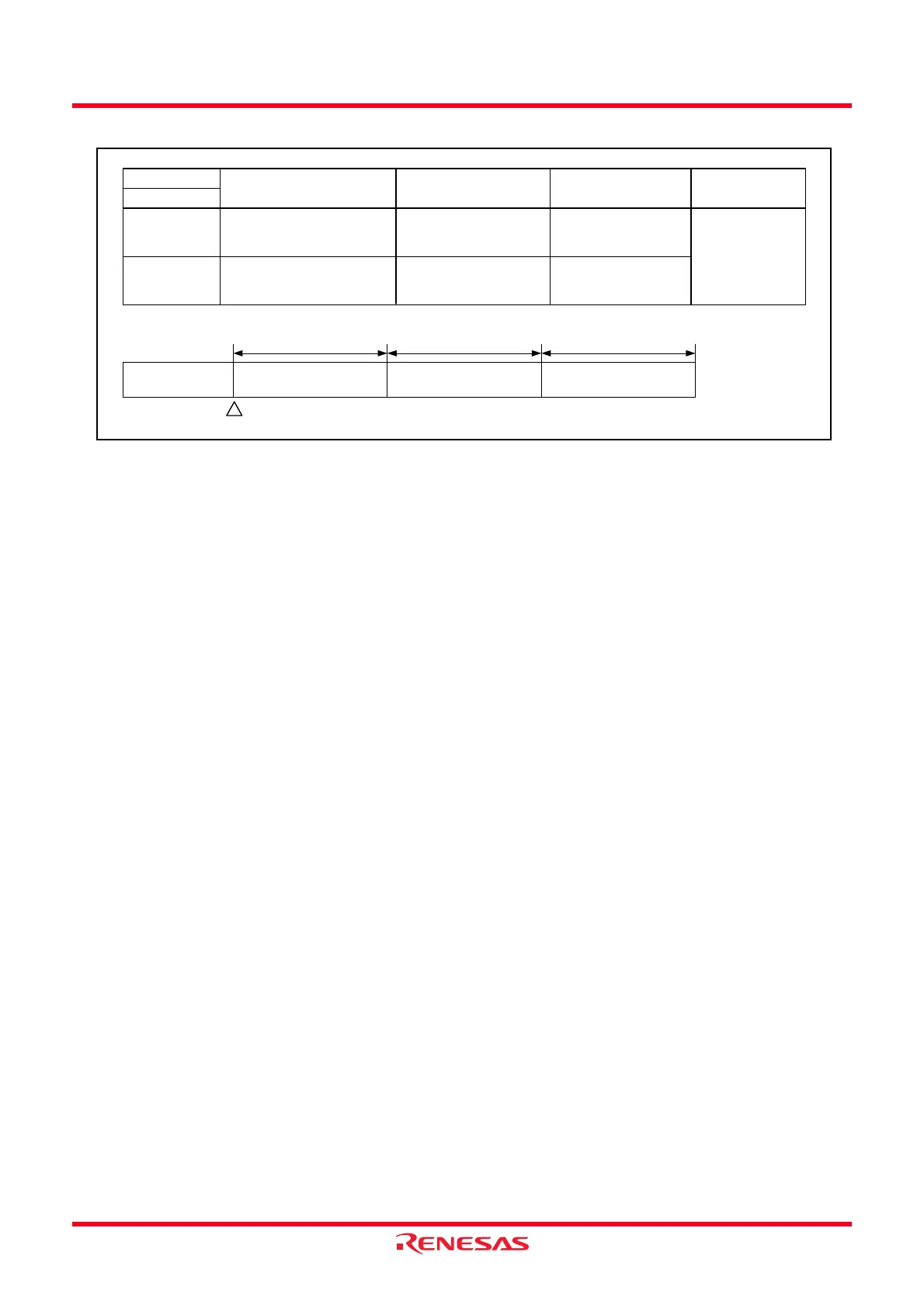

Wait mode

Flash memory activation

sequence

CPU clock restart

sequence

Interrupt sequence

T1 T2 T3

Interrupt request generated

Loading...

Loading...