RL78/G13 CHAPTER 3 CPU ARCHITECTURE

R01UH0146EJ0100 Rev.1.00 162

Sep 22, 2011

3.4.8 Based indexed addressing

[Function]

Based indexed addressing uses the contents of a register pair specified with the instruction word as the base

address, and the content of the B register or C register similarly specified with the instruction word as offset address.

The sum of these values is used to specify the target address.

[Operand format]

Identifier Description

−

[HL+B], [HL+C] (only the space from F0000H to FFFFFH is specifiable)

−

ES:[HL+B], ES:[HL+C] (higher 4-bit addresses are specified by the ES register)

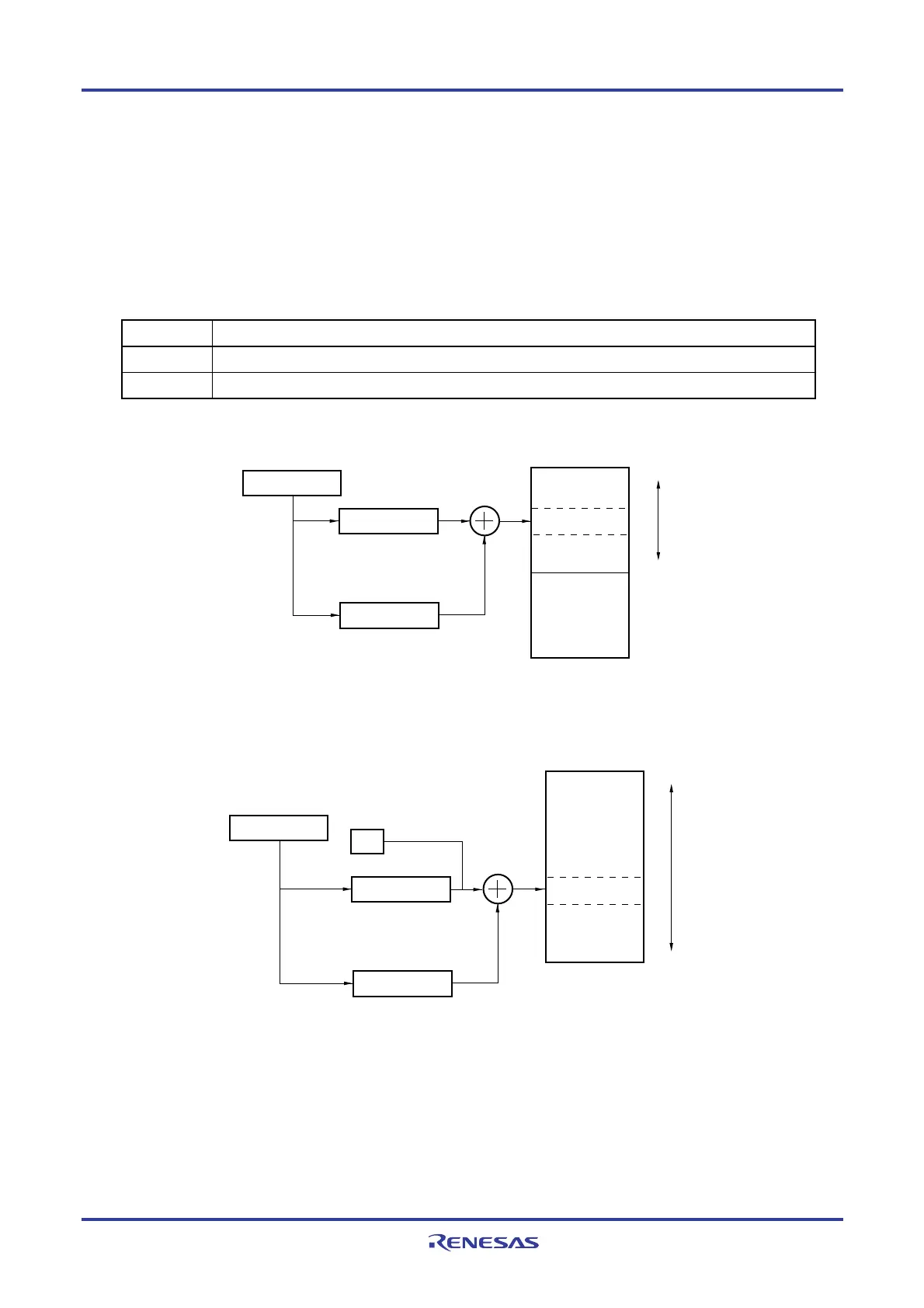

Figure 3-48. Example of [HL+B], [HL+C]

Target memory

Memory

FFFFFH

F0000H

r (B/C)

rp (HL)

OP code

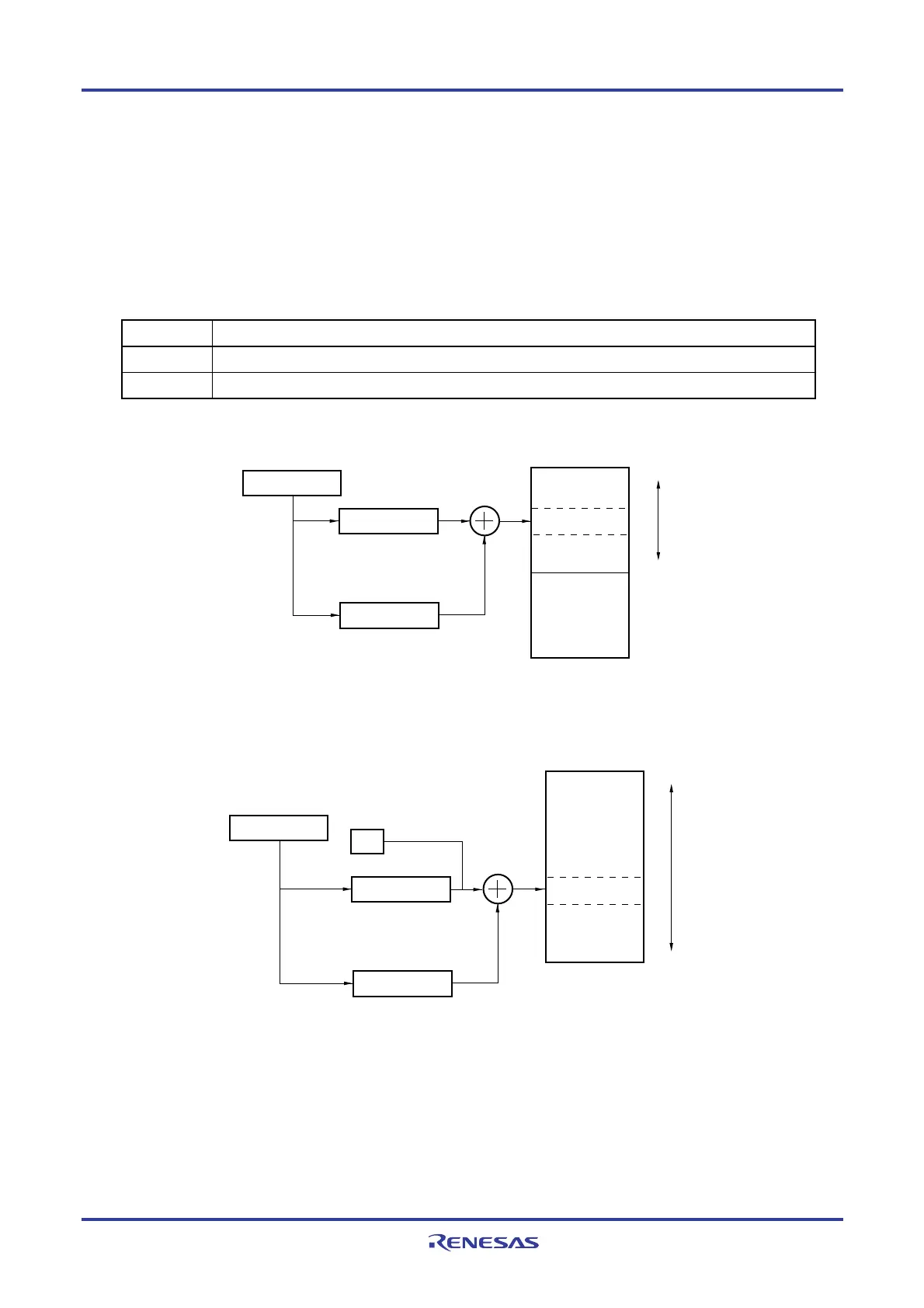

Figure 3-49. Example of ES:[HL+B], ES:[HL+C]

r (B/C)

OP code

rp (HL)

ES

Memory

FFFFFH

00000H

Target memory

Loading...

Loading...