RL78/G13 CHAPTER 15 DMA CONTROLLER

R01UH0146EJ0100 Rev.1.00 816

Sep 22, 2011

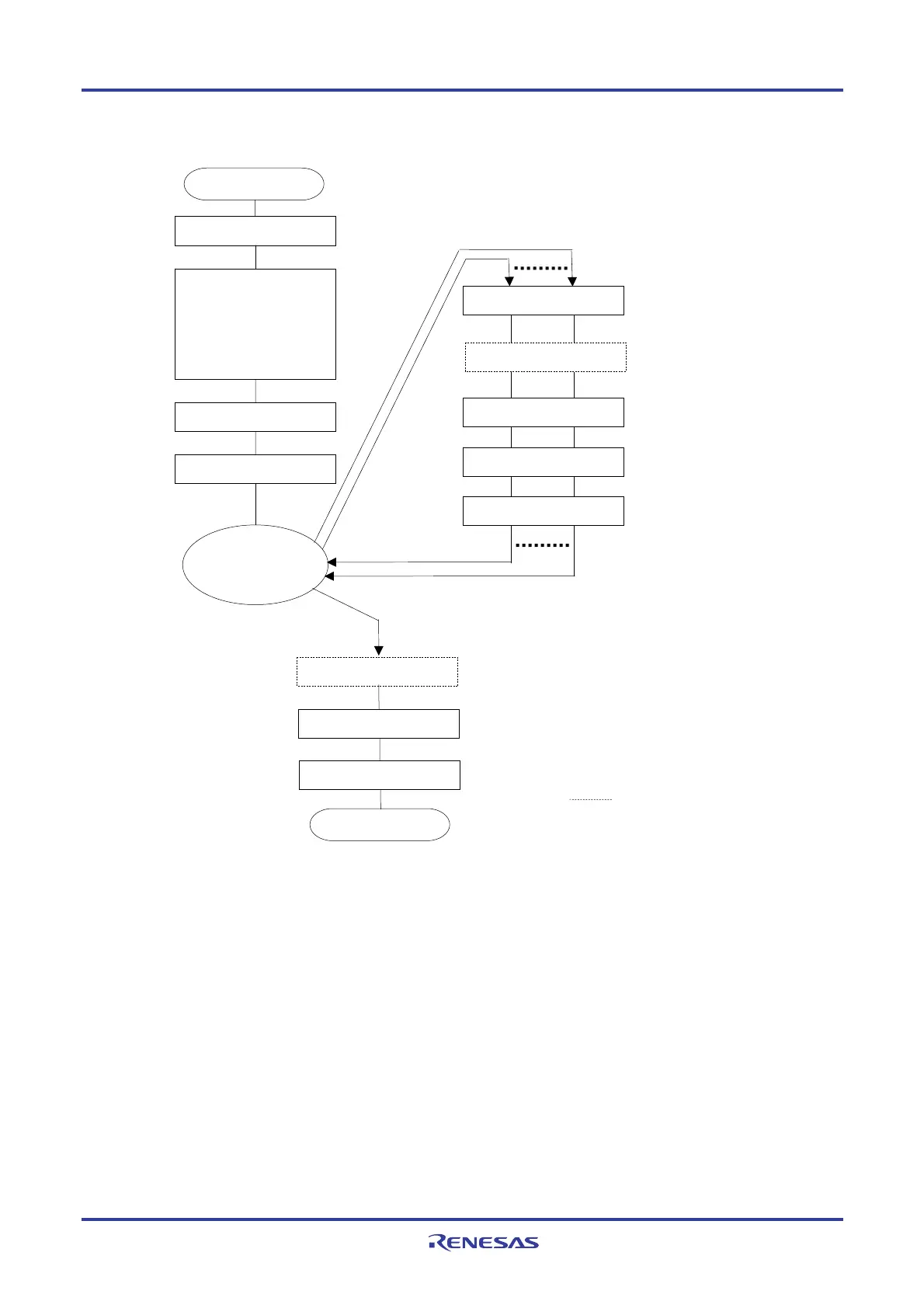

DEN0 = 1

DSA0 = 12H

DRA0 = FE00H

DBC0 = 0040H

DMC0 = 00H

DEN0 = 0

Note

Setting for UART reception

DST0 = 1

User program

processing

STG0 = 1

P10 = 1

P10 = 0

INTSR0 occurs.

INTDMA0

occurs.

DST0 = 0

DMA0 transfer

RETI

Hardware operation

Start

End

RETI

INTSR0 interrupt routine

Figure 15-9. Example of Setting for UART Consecutive Reception + ACK Transmission

Note The DST0 flag is automatically cleared to 0 when a DMA transfer is completed.

Writing the DEN0 flag is enabled only when DST0 = 0. To terminate a DMA transfer without waiting for

occurrence of the interrupt of DMA0 (INTDMA0), set the DST0 bit to 0 and then the DEN0 bit to 0 (for details,

refer to 15.5.5 Forced termination by software).

Remark This is an example where a software trigger is used as a DMA start source.

If ACK is not transmitted and if only data is consecutively received from UART, the UART reception end

interrupt (INTSR0) can be used to start DMA for data reception.

Loading...

Loading...