RL78/G13 CHAPTER 22 SAFETY FUNCTIONS

R01UH0146EJ0100 Rev.1.00 904

Sep 22, 2011

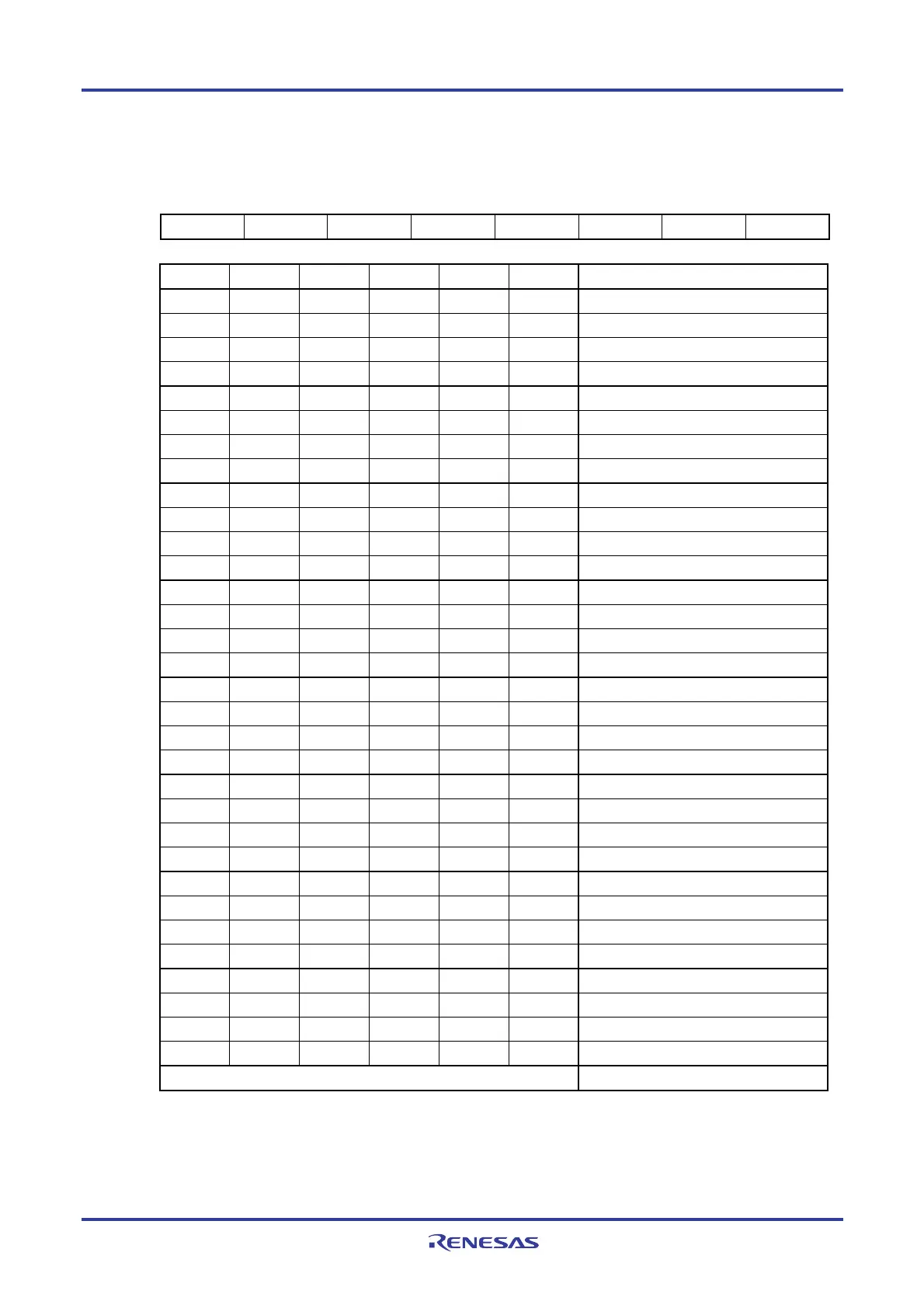

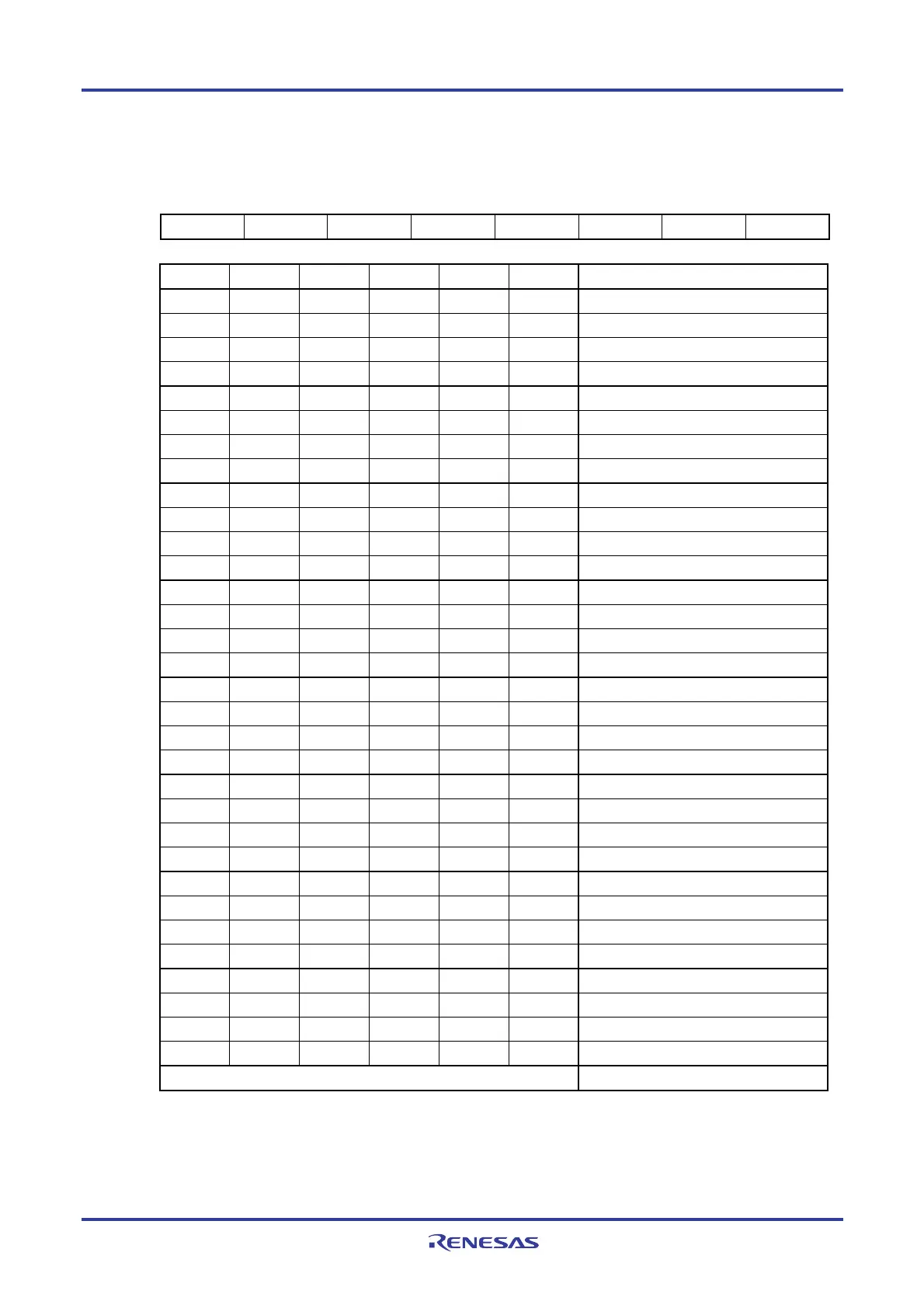

Figure 22-1. Format of Flash Memory CRC Control Register (CRC0CTL) (2/2)

Address: F02F0H After reset: 00H R/W

Symbol <7> 6 5 4 3 2 1 0

CRC0CTL CRC0EN 0 FEA5 FEA4 FEA3 FEA2 FEA1 FEA0

FEA5 FEA4 FEA3 FEA2 FEA1 FEA0 High-speed CRC operation range

0 0 0 0 0 0 0 to 3FFBH (16 K to 4 bytes)

0 0 0 0 0 1 0 to 7FFBH (32 K to 4 bytes)

0 0 0 0 1 0 0 to BFFBH (48 K to 4 bytes)

0 0 0 0 1 1 0 to FFFBH (64 K to 4 bytes)

0 0 0 1 0 0 0 to 13FFBH (80 K to 4 bytes)

0 0 0 1 0 1 0 to 17FFBH (96 K to 4 bytes)

0 0 0 1 1 0 0 to 1BFFBH (112 K to 4 bytes)

0 0 0 1 1 1 0 to 1FFFBH (128 K to 4 bytes)

0 0 1 0 0 0 0 to 23FFBH (144 K to 4 bytes)

0 0 1 0 0 1 0 to 27FFBH (160 K to 4 bytes)

0 0 1 0 1 0 0 to 2BFFBH (176 K to 4 bytes)

0 0 1 0 1 1 0 to 2FFFBH (192 K to 4 bytes)

0 0 1 1 0 0 0 to 33FFBH (208 K to 4 bytes)

0 0 1 1 0 1 0 to 37FFBH (224 K to 4 bytes)

0 0 1 1 1 0 0 to 3BFFBH (240 K to 4 bytes)

0 0 1 1 1 1 0 to 3FFFBH (256 K to 4 bytes)

0 1 0 0 0 0 0 to 43FFBH (272 K to 4 bytes)

0 1 0 0 0 1 0 to 47FFBH (288 K to 4 bytes)

0 1 0 0 1 0 0 to 4BFFBH (304 K to 4 bytes)

0 1 0 0 1 1 0 to 4FFFBH (320 K to 4 bytes)

0 1 0 1 0 0 0 to 53FFBH (336 K to 4 bytes)

0 1 0 1 0 1 0 to 57FFBH (352 K to 4 bytes)

0 1 0 1 1 0 0 to 5BFFBH (368 K to 4 bytes)

0 1 0 1 1 1 0 to 5FFFBH (384 K to 4 bytes)

0 1 1 0 0 0 0 to 63FFBH (400 K to 4 bytes)

0 1 1 0 0 1 0 to 67FFBH (416 K to 4 bytes)

0 1 1 0 1 0 0 to 6BFFBH (432 K to 4 bytes)

0 1 1 0 1 1 0 to 6FFFBH (448 K to 4 bytes)

0 1 1 1 0 0 0 to 73FFBH (464 K to 4 bytes)

0 1 1 1 0 1 0 to 77FFBH (480 K to 4 bytes)

0 1 1 1 1 0 0 to 7BFFBH (496 K to 4 bytes)

0 1 1 1 1 1 0 to 7FFFBH (512 K to 4 bytes)

Other than the above Setting prohibited

Remark Input the expected CRC operation result value to be used for comparison in the lowest 4 bytes of the flash

memory. Note that the operation range will thereby be reduced by 4 bytes.

Loading...

Loading...