MB95630H Series

MN702-00009-2v0-E FUJITSU SEMICONDUCTOR LIMITED 511

CHAPTER 24 I

2

C BUS INTERFACE

24.6 Operations and Setting Procedure Example

24.6.2 Function to Wake up the MCU from Standby Mode

The wakeup function enables the I

2

C macro to be accessed while the MCU is in

stop or watch mode.

■ Function to Wake Up the MCU from Standby Mode

The I

2

C macro includes a function to wake up the MCU from standby mode. The function is

enabled by writing "1" to the IBCR0n:WUE bit.

With the MCU in stop mode or watch mode and the IBCR0n:WUE bit set to "1", if a start

condition is detected on the I

2

C bus, the wakeup interrupt request flag bit (IBCR0n:WUF) is

set to "1" and the wakeup interrupt request is generated to wake up the MCU from stop/watch

mode.

• Set IBCR0n:WUE to "1" immediately before setting the MCU to stop or watch mode.

Similarly, clear IBCR0n:WUE (by writing "0") after the MCU wakes up from stop or watch

mode so that I

2

C operation can restart as soon as possible.

• The wakeup function only applies to the MCU stop and watch modes.

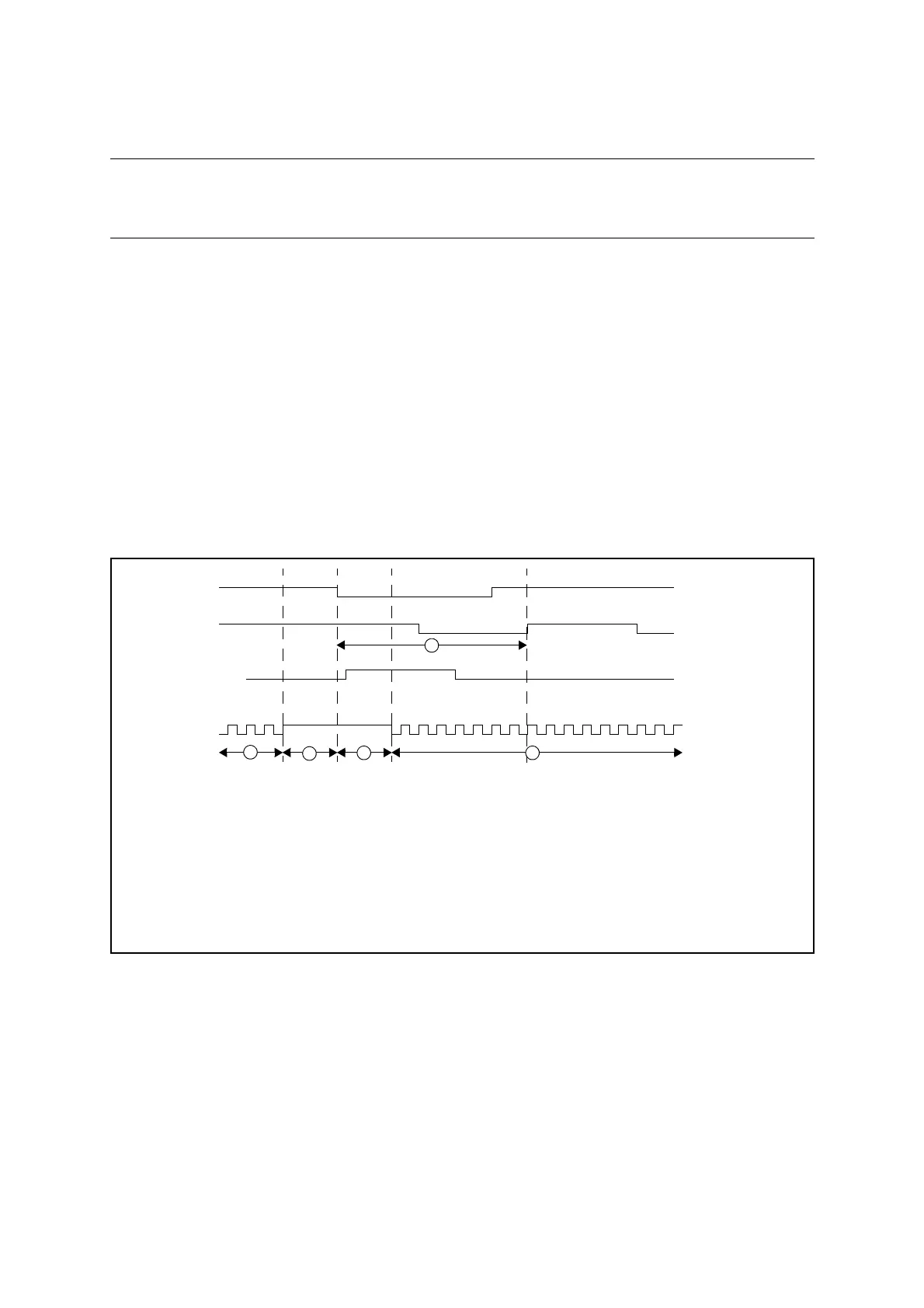

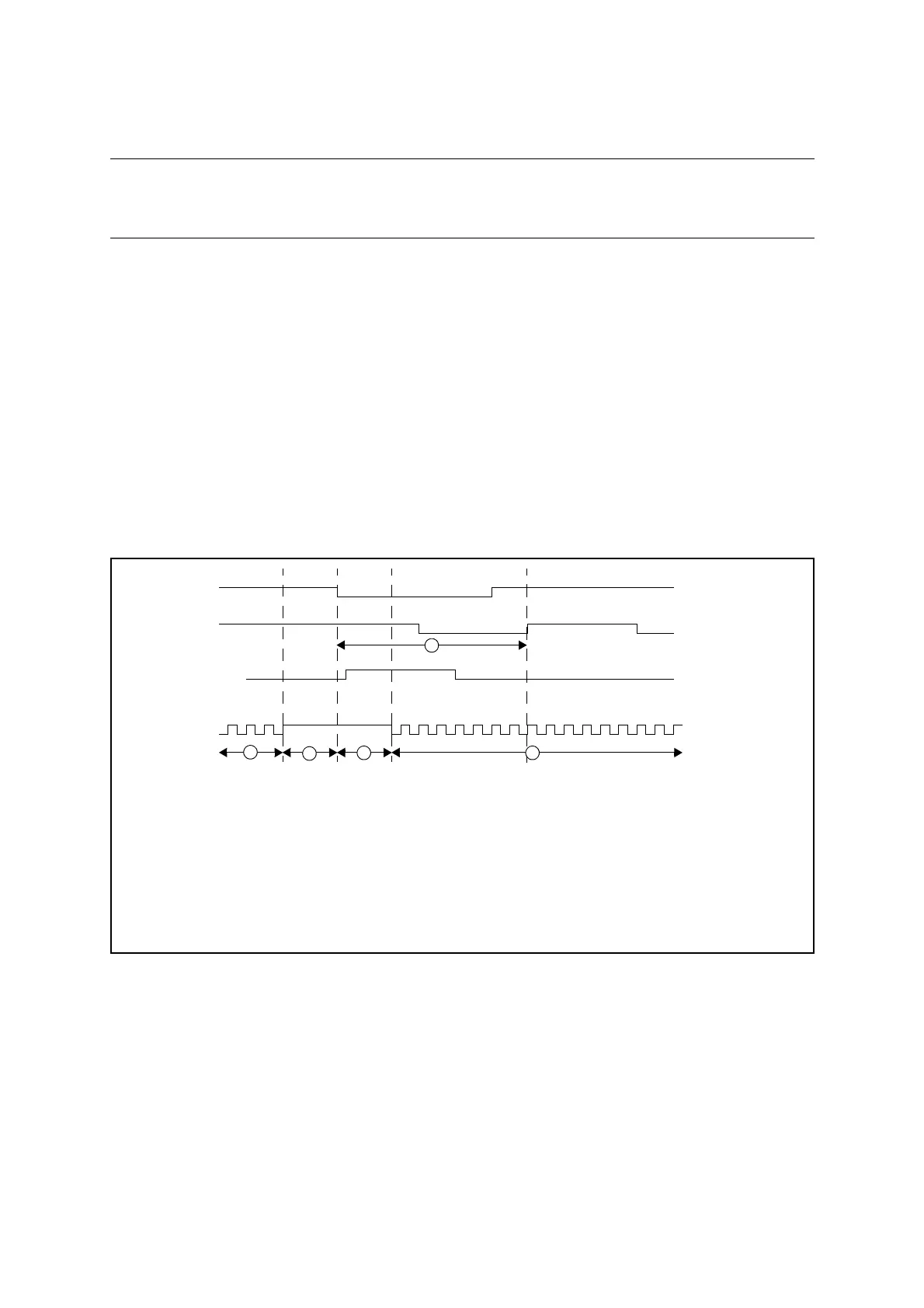

Figure 24.6-7 Comparison of Normal I

2

C Operation and Wakeup Operation

SDAn

SCLn

IRQ by

IBCR0n:WUF

Machine

Clock

1

2

3 4

5

➀ Set the IBCR0n:WUE bit to "1" immediately before entering stop/watch mode and make sure that IBSRn:BB = 0.

➁ Set the MCU to stop/watch mode and the machine clock stops.

➂ Detect a start condition in stop mode or watch mode. IBCR0n:WUF is set to 1 and a wakeup IRQ is generated. In stop

mode, after the oscillation stabilization wait time, the MCU wakes up and enters the clock mode used before entering stop

mode or watch mode.

➃ Clear the IBCR0n:WUE bit to "0" so that I

2

C can restart the normal operation, and clear the IBCR0n:WUF bit to "0" to clear

the wakeup interrupt.

➄ To receive the data byte correctly, the SCLn must be released in the first cycle after 100 μs (assuming a minimum

oscillation stabilization wait time of 100 μs) from the start of I

2

C transmission (falling edge detection of SDAn).

Loading...

Loading...