R8C/20 Group, R8C/21 Group 12. Interrupts

Rev.2.00 Aug 27, 2008 Page 107 of 458

REJ09B0250-0200

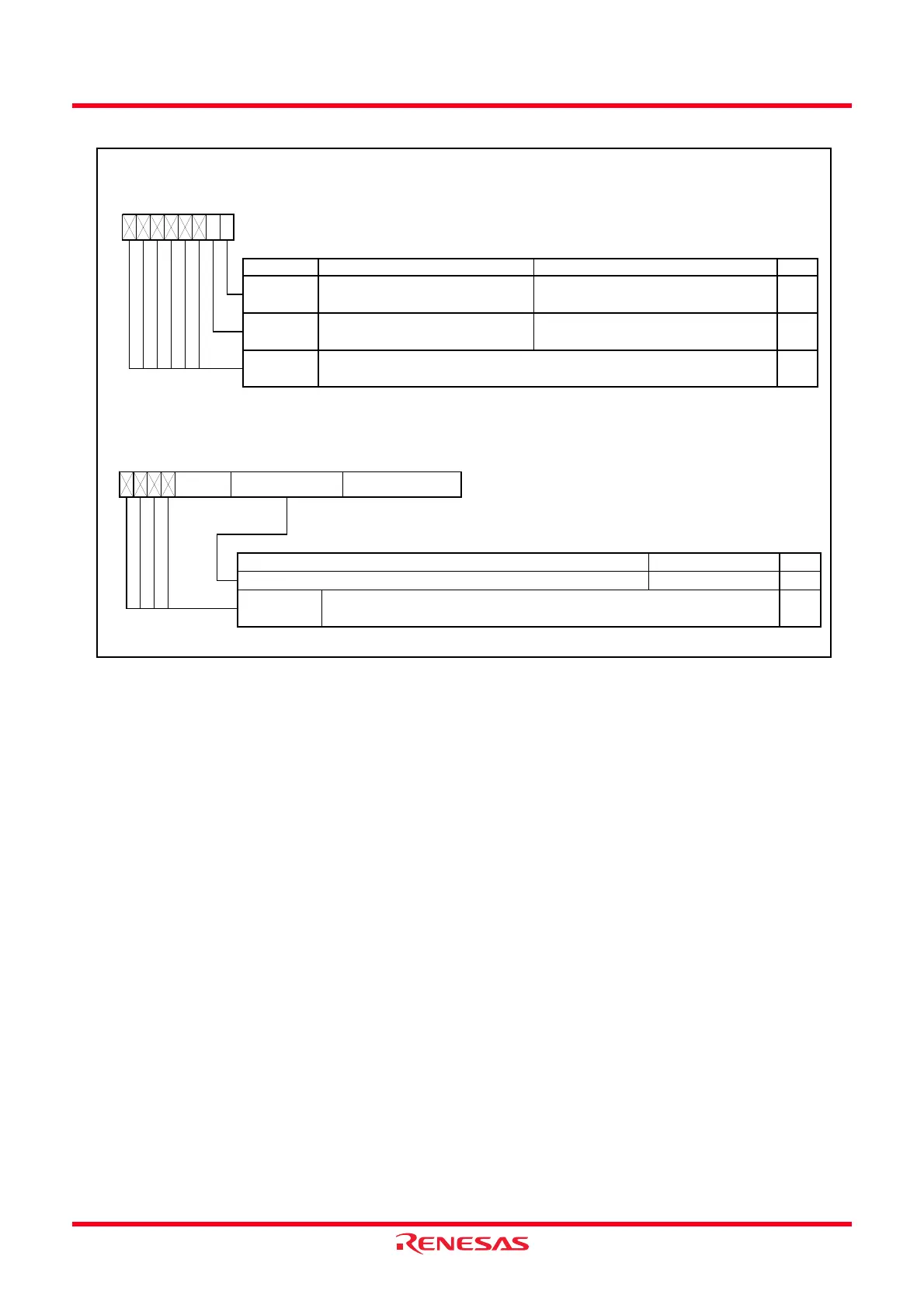

Figure 12.18 Registers AIER and RMAD0 to RMAD1

ddress Match Interrupt Enable Registe

Symbol Address After Reset

AIER

0013h 00h

Bit Symbol Bit Name Function RW

—

(b7-b2)

—

Nothing is assigned. If necessary, set to 0.

When read, the content is 0.

b7 b6 b5 b4

0 : Disable

1 : Enable

RW

b3 b2 b1 b0

Address match interrupt 0 enable bit 0 : Disable

1 : Enable

RW

AIER1

Address match interrupt 1 enable bit

AIER0

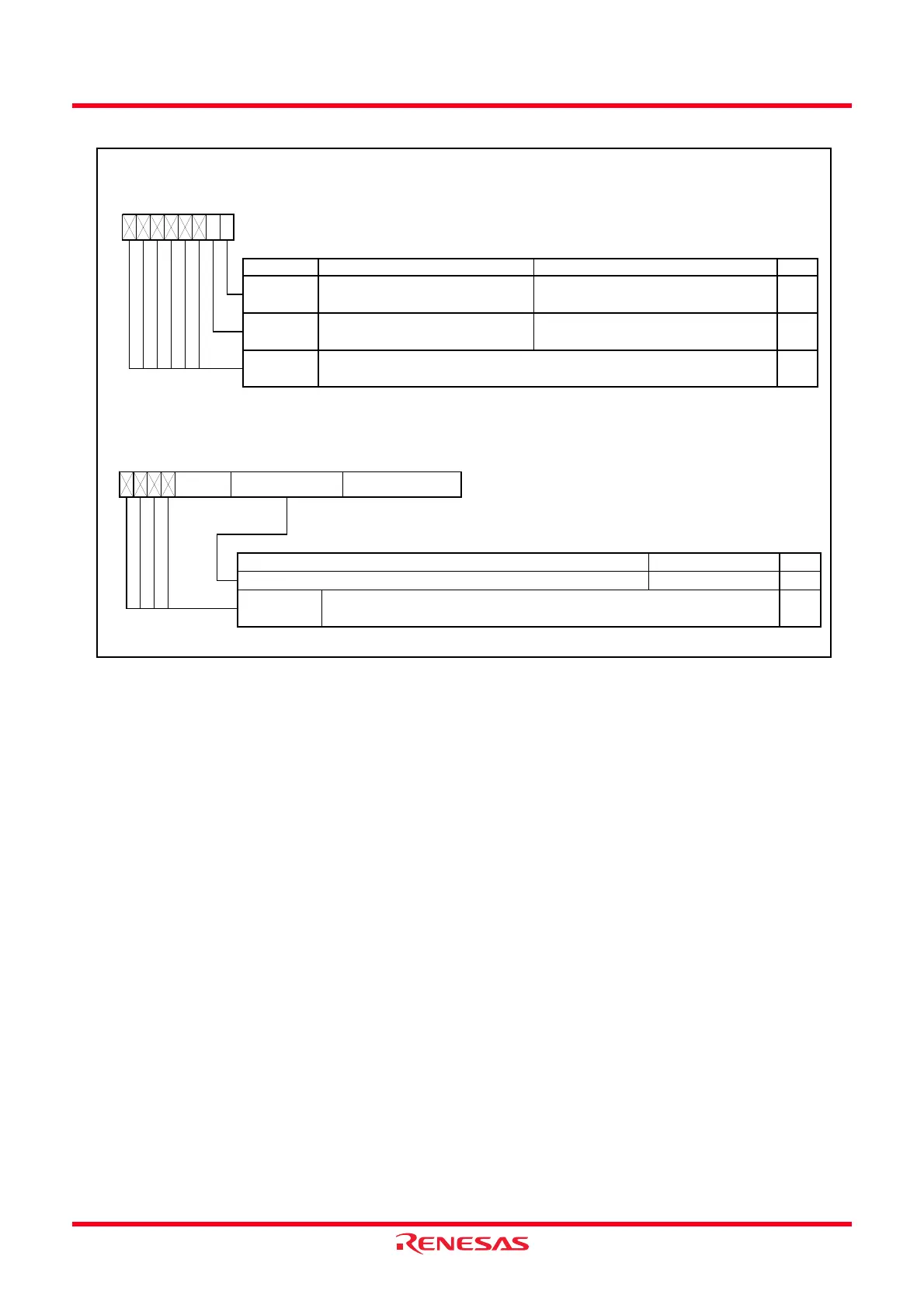

Address Match Interrupt Register i (i = 0 or 1)

b0

Symbol Address After Reset

RMAD0

0012h-0010h 000000h

RMAD1

0016h-0014h 000000h

Setting Range RW

(b16)

b0

(b19)

b3

(b23)

b7

RW

—

—

(b7-b4)

Nothing is assigned. If necessary, set to 0.

When read, the content is 0.

Address setting register for address match interrupt

(b15)

b7

(b8)

b0 b7

00000h to FFFFFh

Function

Loading...

Loading...