R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 320 of 458

REJ09B0250-0200

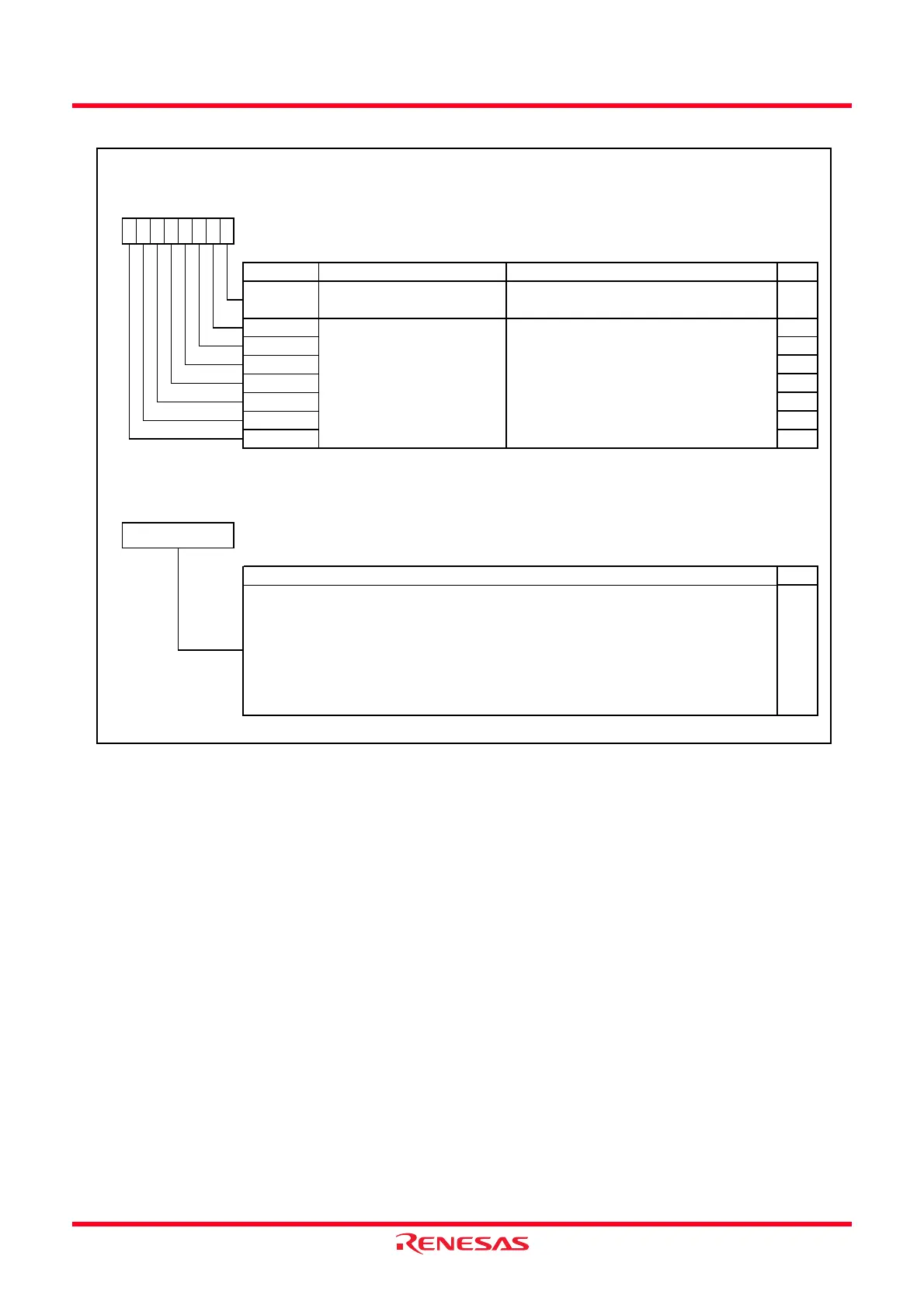

Figure 16.29 Registers SAR and ICDRT

Slave Address Register

Symbol Address After Reset

SAR

00BDh 00h

Bit Symbol Bit Name Function RW

RW

Slave address 6 to 0 Set the different address from the other slave

devices w hich are connected to the I

2

C bus.

When the 7 high-order bits of the first frame

transmitted after the starting condition match

the SVA0 to SVA6 bits in slave mode of the I

2

C

bus format, the MCU operates as a slave

device.

RW

RW

RW

RW

SVA3

SVA6

SVA5

SVA4

RW

RW

FS

Format select bit 0 : I

2

C bus format

1 : Clock synchronous serial format

RW

SVA2

SVA0

SVA1

b7 b6 b0b1b5 b3 b2b4

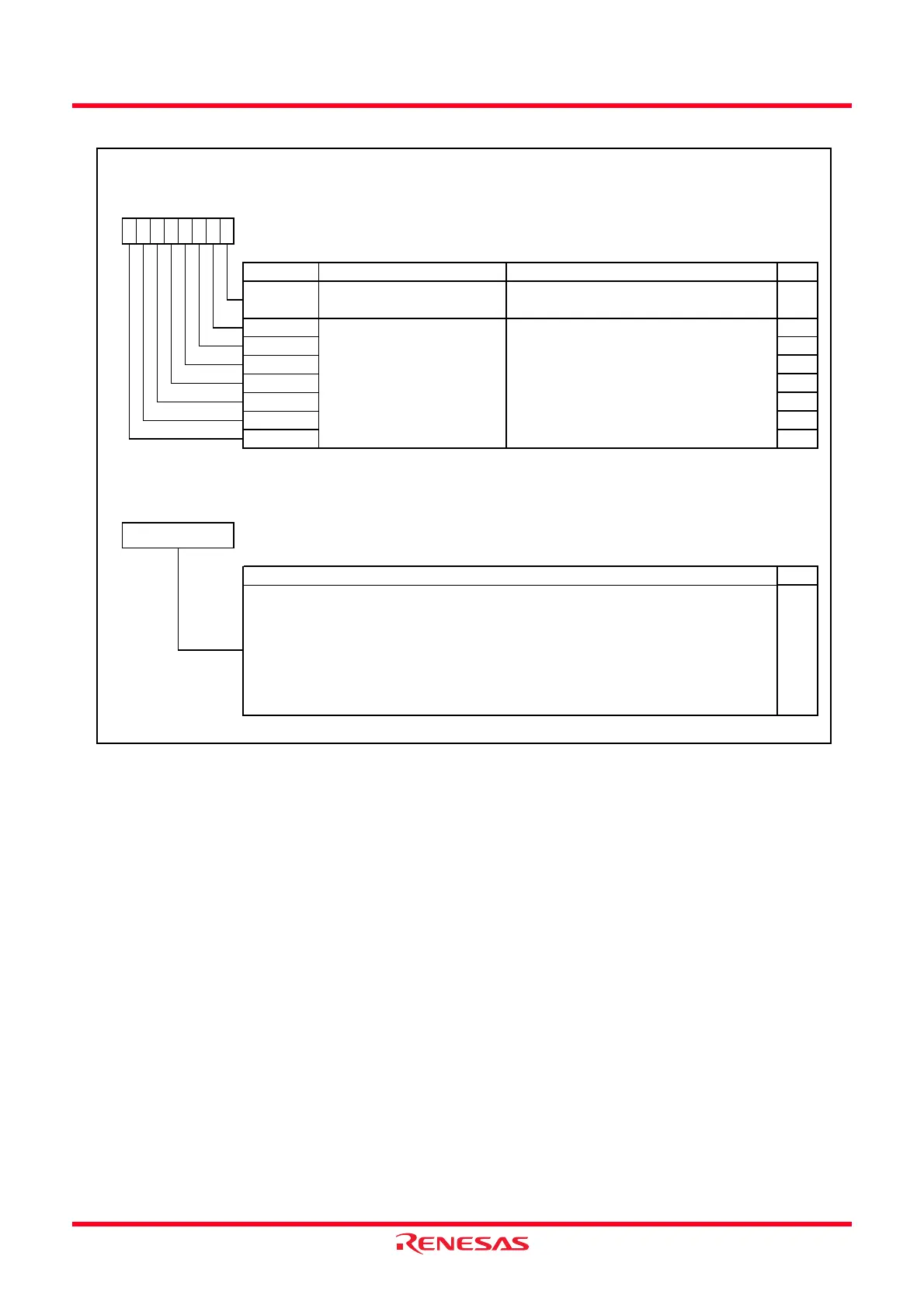

IIC Bus Transmit Data Register

Symbol Address After Reset

ICDRT

00BEh FFh

RW

RW

Function

Store transmit data

When detecting that the ICDRS register is empty, the stored transmit data is transferred to the

ICDRS register and the starts transmit data.

When the next transmit data is w ritten to the ICDRT register during transmitting the data of the

ICDRS register, continuous transmit is enabled. When the MLS bit in the ICMR register is set to

1 (data transferred by LSB-first) and after the data is w ritten to the ICDRT register, the MSB

and LSB inverted data is read.

b0b7

Loading...

Loading...