RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 167

Dec 22, 2016

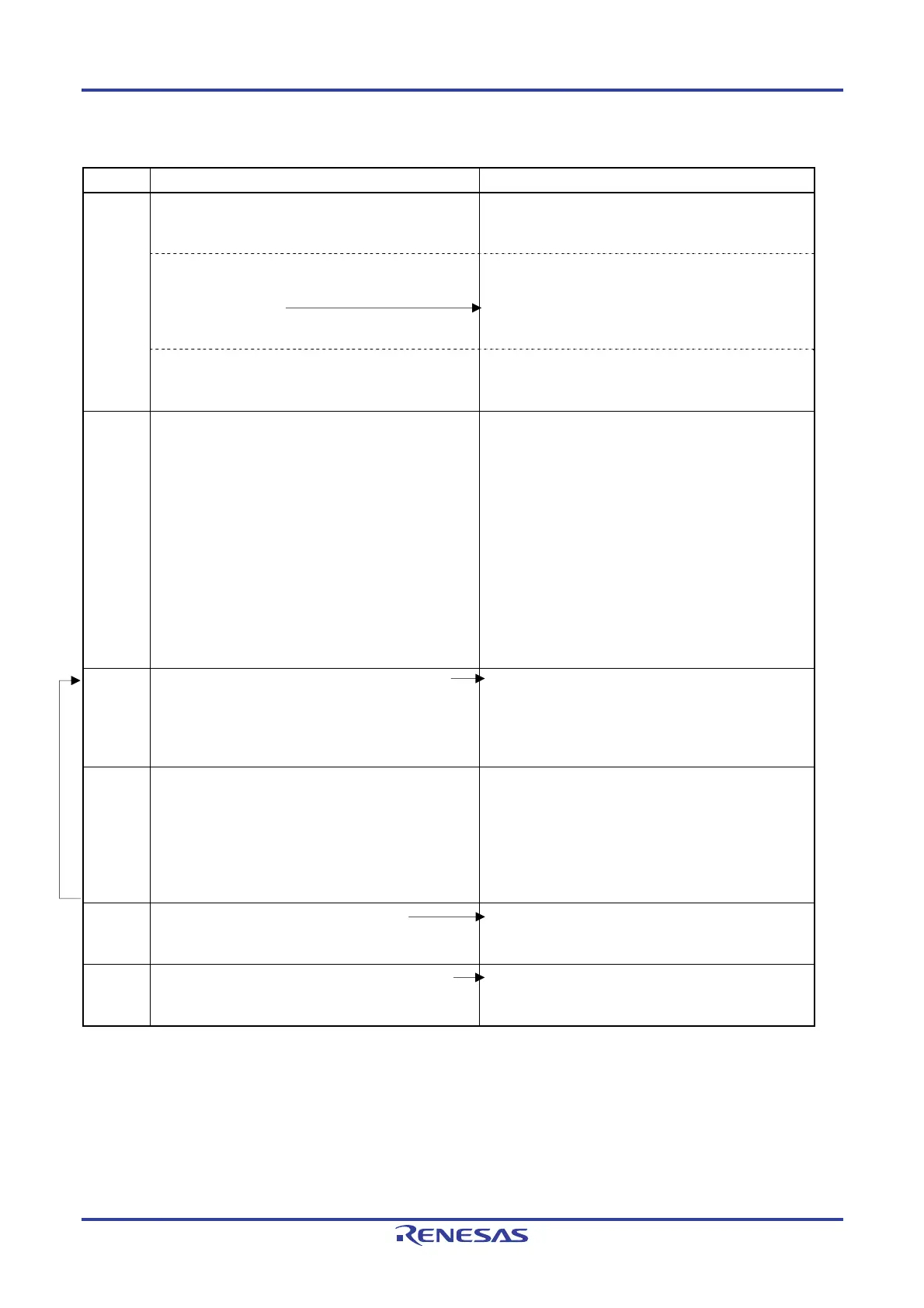

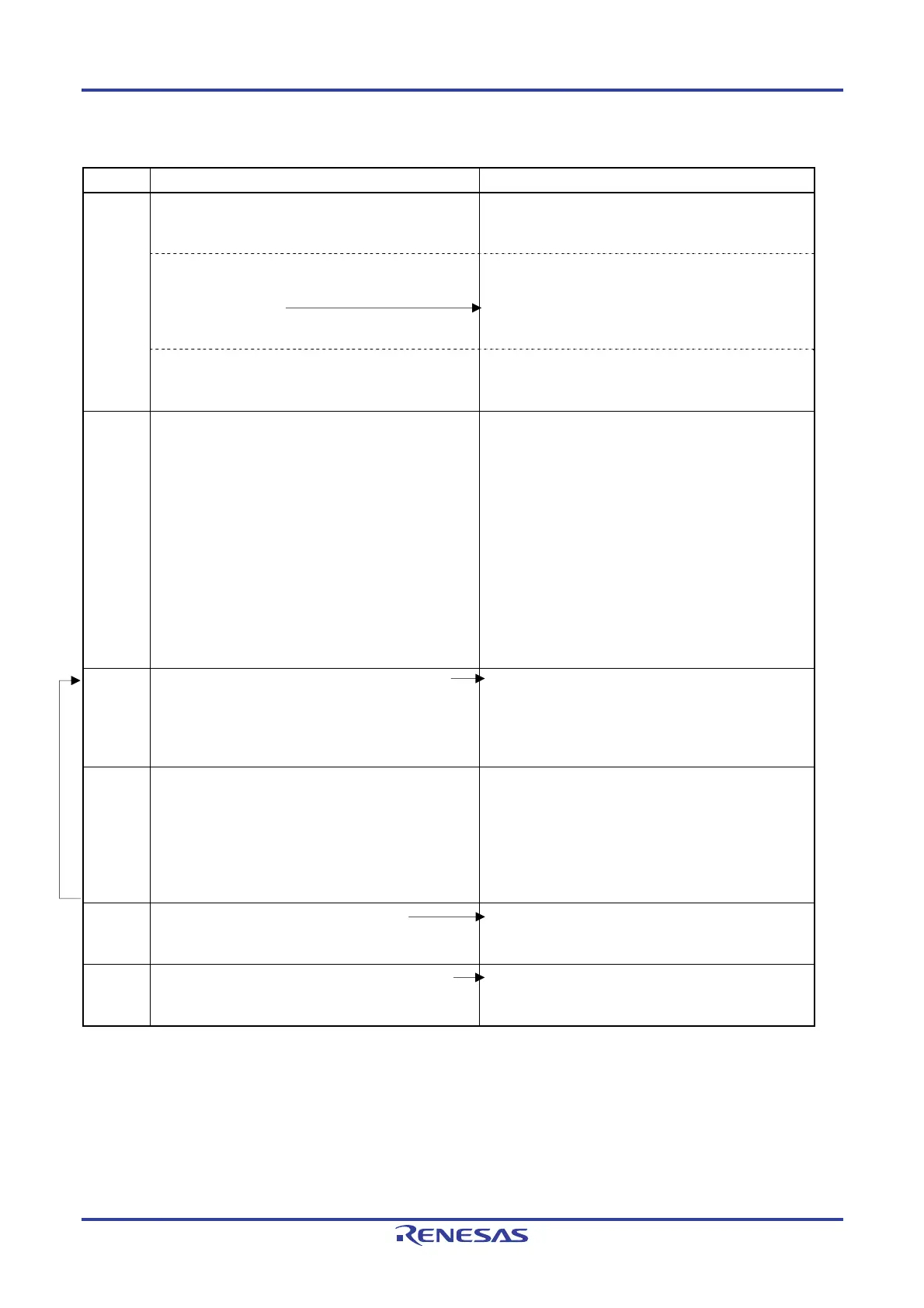

Figure 6-47. Procedure for Operating External Event Counter

Software Operation Hardware Status

TAU

default

setting

Power-off status

(Clock supply is stopped and writing to SFR of the TAU

is disabled.)

Sets the TAU0EN bit of peripheral enable register 0

(PER0) to 1 (when the TAU0EN bit is 0, read/write

operation is disabled).

Power-on status. Each channel stops operating.

(Clock supply is started and writing to SFR of the TAU is

enabled.)

Sets timer clock select register 0 (TPS0).

Determines operating clock (CK00 and CK01) for each

channel.

Channel

default

setting

Sets noise filter enable register 1 (NFEN1).

Sets timer mode register 0n (TMR0n) (determines

operation mode for each channel and selects the

detection edge).

Sets number of counts in the timer data register 0n

(TDR0n) (for the access procedure to the TDR0nH and

TDR0nL registers, see 6.2.2 Timer data register 0n

(TDR0n)).

Clears the target bit of timer output mode register 0

(TOM0) to 0 (master channel output mode).

Clears the target bit of the TOL0 register to 0.

Clears the target bit of timer output enable register 0

(TOE0) to 0.

Channel stops operating.

Operation

start

Sets the target bit of TS0 register to 1.

The target bit of TS0 register automatically returns to 0

because it is a trigger bit.

The target bit of TE0 register is set to 1, and count

operation starts.

Value of the TDR0n register is loaded to timer count

register 0n (TCR0n) and detection of the TI0n pin input

edge is awaited.

During

operation

The set value of the TDR0n register can be changed.

The TCR0n register can always be read (for the access

procedure to the TCR0nH and TCR0nL registers, see

6.2.1 Timer counter register 0n (TCR0n)).

The set values in the target bits of the TMR0n, TO0,

TOE0, TOM0, and TOL0 registers cannot be changed.

Counter (TCR0n) counts down each time input edge of the

TI0n pin has been detected. When count value reaches

0000H, the value of the TDR0n register is loaded to the

TCR0n register again, and the count operation is

continued. By detecting TCR0n = 0000H, the INTTM0n is

generated.

After that, the above operation is repeated.

Operation

stop

Sets the target bit of TT0 register to 1.

The target bit of TT0 automatically returns to 0

because it is a trigger bit.

The target bit of TE0 register is cleared to 0, and count

operation stops.

The TCR0n register holds count value and stops.

TAU

stop

Clears the TAU0EN bit of the PER0 register to 0.

Power-off status

(Clock supply is stopped and SFR of the TAU is

initialized.)

Remark n: Channel number

n = 0, 1 (for 10-pin products); n = 0 to 3 (for 16-pin products)

Operation is resumed.

Loading...

Loading...