RL78/G10 CHAPTER 7 12-BIT INTERVAL TIMER

R01UH0384EJ0311 Rev. 3.11 227

Dec 22, 2016

7.3.3 Interval timer control register (ITMCH, ITMCL)

This register is used to set up the starting and stopping of the 12-bit interval timer operation and to specify the timer

compare value.

Set the eight lower-order bits (ITCMP7 to ITCMP0) of the value for comparison in the ITMCL register and then set the

four higher-order bits (ITCMP11 to ITCMP8) of the value for comparison and make the setting to stop or start counter

operation in the ITMCH register.

The ITMCH and ITMCL registers can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets the ITMCH and ITMCL registers to 0FH and FFH, respectively.

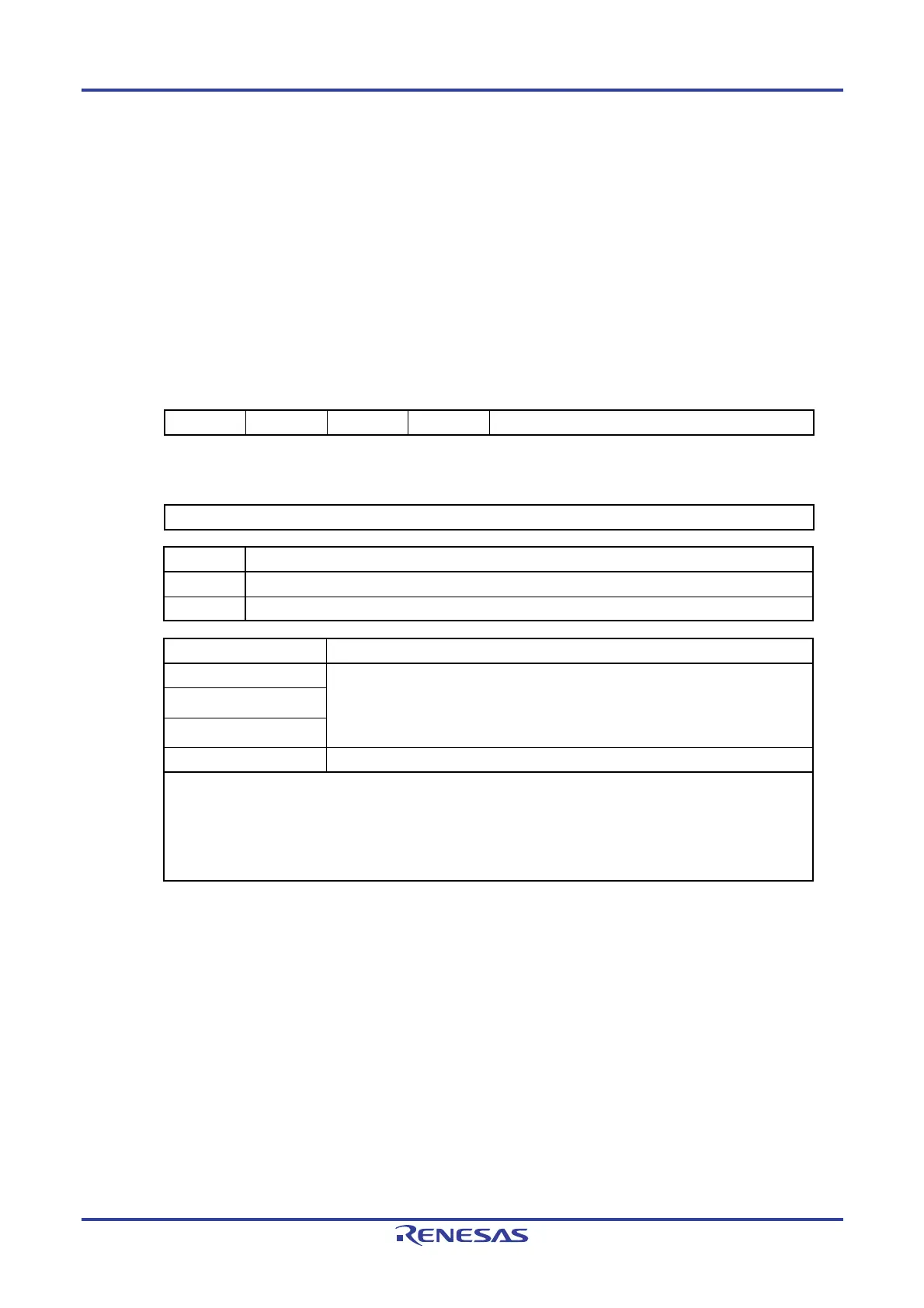

Figure 7-4. Format of Interval Timer Control Register (ITMCH, ITMCL)

Address: FFF91H After reset: 0FH R/W

Symbol 7 6 5 4 3 to 0

ITMCH RINTE 0 0 0 ITCMP11 to ITCMP8

Address: FFF90H After reset: FFH R/W

Symbol 7 6 5 4 3 2 1 0

ITMCL ITCMP7 to ITCMP0

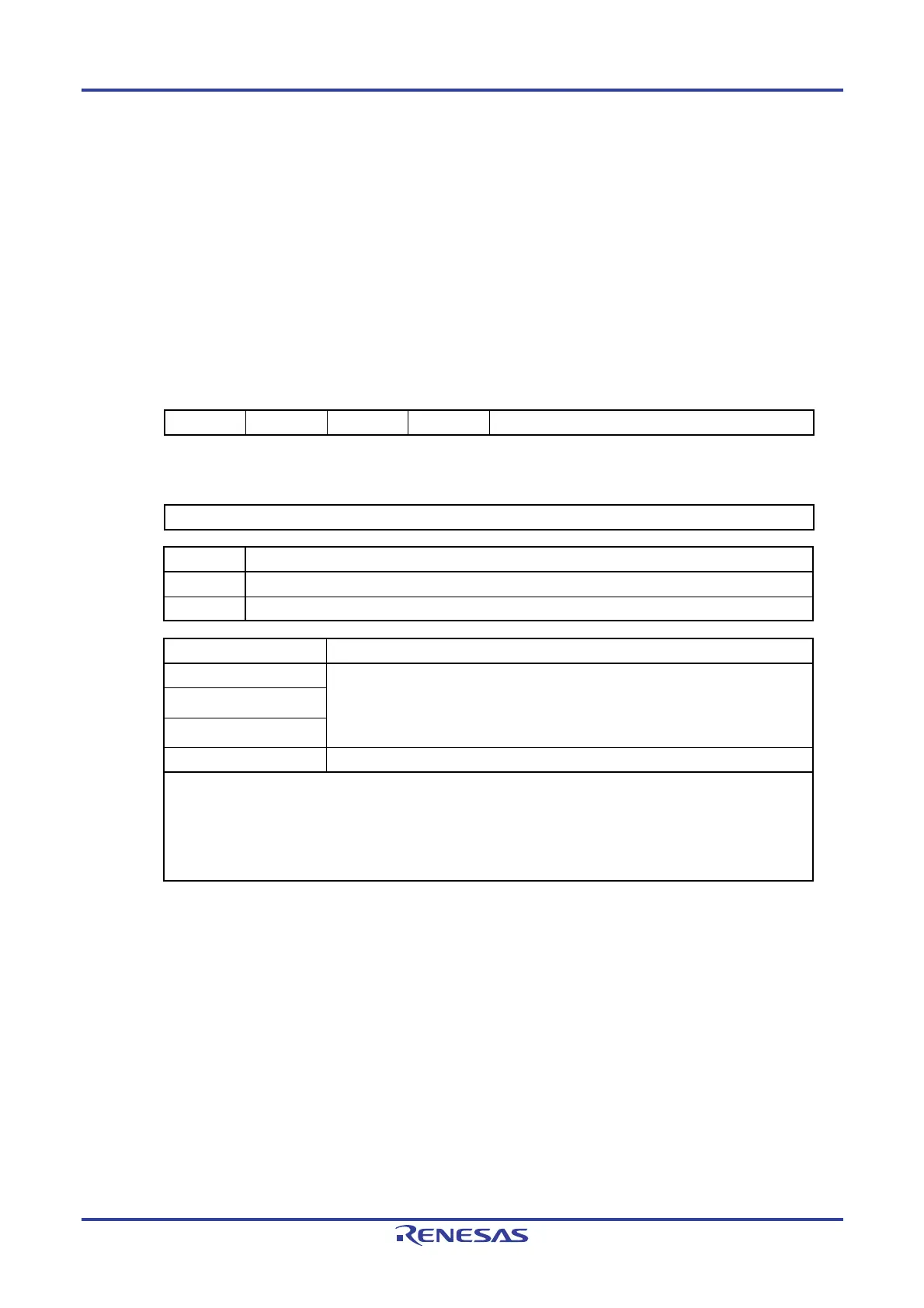

RINTE 12-bit interval timer operation control

0 Count operation stopped (count clear)

1 Count operation started

ITCMP11 to ITCMP0 Specification of the 12-bit interval timer compare value

001H

These bits generate an interrupt at the fixed cycle (count clock cycles x (ITCMP

setting + 1)).

• • •

FFFH

000H Setting prohibited

Example interrupt cycles when 001H or FFFH is specified for ITCMP11 to ITCMP0

• ITCMP11 to ITCMP0 = 001H, count clock: when f

IL = 15 kHz

1/15 [kHz] × (1 + 1) ÷ 0.1333 [ms] = 133.3 [

μ

s]

• ITCMP11 to ITCMP0 = FFFH, count clock: when f

IL = 15 kHz

1/15 [kHz] × (4095 + 1) ÷ 273 [ms]

Cautions 1. Set the TMKAMK flag to 1 to disable processing of the INTIT interrupt before stopping

the counter (by clearing the RINTE bit to 0). Clear the TMKAIF flag to 0 to enable INTIT

interrupt processing before restarting counter operation (by setting the RINTE bit to 1).

2. The value read from the RINTE bit is applied one count clock cycle after setting the

RINTE bit to 1.

3. When setting the RINTE bit after returned from standby mode and entering standby

mode again, confirm that the written value of the RINTE bit is reflected, or wait that

more than one clock of the count clock has elapsed after returned from standby mode.

Then enter standby mode.

4. Only change the setting of the ITCMP11 to ITCMP0 bits when the counting operation is

stopped (RINTE = 0).

However, it is possible to change the settings of the ITCMP11 to ITCMP8 bits at the

same time as when changing the setting of the RINTE bit from 0 to 1 or 1 to 0.

Loading...

Loading...