RL78/G10 CHAPTER 10 A/D CONVERTER

R01UH0384EJ0311 Rev. 3.11 257

Dec 22, 2016

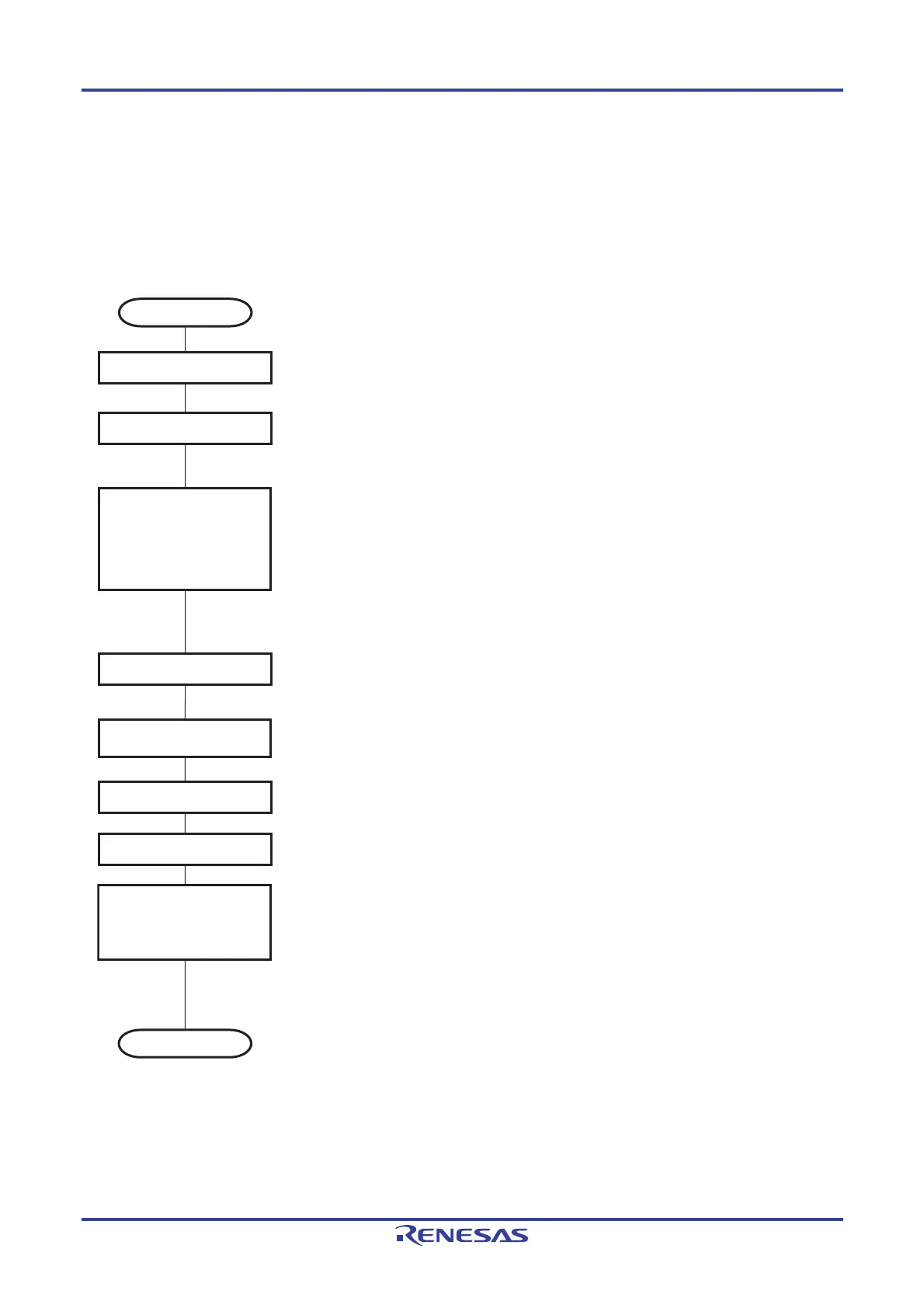

10.7 A/D Converter Setup Flowchart

The A/D converter setup flowchart is described below.

10.7.1 Setting up A/D conversion of voltages on ANI0 to ANI6

Figure 10-15. Setting Up A/D Conversion of Voltages on ANI0 to ANI6

Start of setup

The ADCEN bit of the PER0 register is set (1), and a clock is provided to the A/D converter.

The ports (ANI0 to ANI6

Note1

) to be A/D converted are set to analog input.

•

Set the bits in the PMC0 and PM0 registers to 1.

The conversion time and each mode of the A/D converter are set.

•

A/D converter mode register 0 (ADM0)

FR1, FR0, and LV0 bits: These bits are used to select the A/D conversion time.

•

A/D converter mode register 2 (ADM2)

ADTYP bit: This bit is used to select 10-bit or 8-bit resolution.

•

Analog input channel specification register (ADS)

ADS2

Note2

, ADS1, and ADS0 bits:

These bits are used to select ANI0 to ANI6

Note 1

as the target of A/D conversion.

The operation of the A/D voltage comparator is started.

The stabilization wait time (0.1

µ

s) is counted by the software.

•

The ADCE bit of the ADM0 register is set (1),

and the system enters the conversion standby status.

A/D conversion ends. The conversion result is stored in the ADCRH and ADCRL registers.

•

A/D conversion result higher-order bit storage register (ADCRH): Eight higher-order bits

•

A/D conversion result lower-order bit storage register (ADCRL): Two lower-order bits

At the same time, the A/D conversion end interrupt request signal (INTAD) is generated,

and the ADCS bit of the ADM0 register is automatically cleared (0) (conversion standby status).

After counting up to the stabilization wait time ends, the ADCS bit of the ADM0

register is set (1) and A/D conversion starts.

End

Setting PER0 register

Setting PMC0 and PM0 registers

•

Setting ADM0 register

•

Setting ADM2 register

•

Setting ADS register

(The order of the settings

is irrelevant.)

Setting ADCE bit

A/D conversion operation

End of A/D conversion

Storage of conversion results

in the ADCRH and ADCRL

registers

Setting ADCS bit

A/D voltage stabilization

wait time count

Notes 1. For 10-pin products, ANI0 to ANI3.

2. 16-pin products only.

Loading...

Loading...