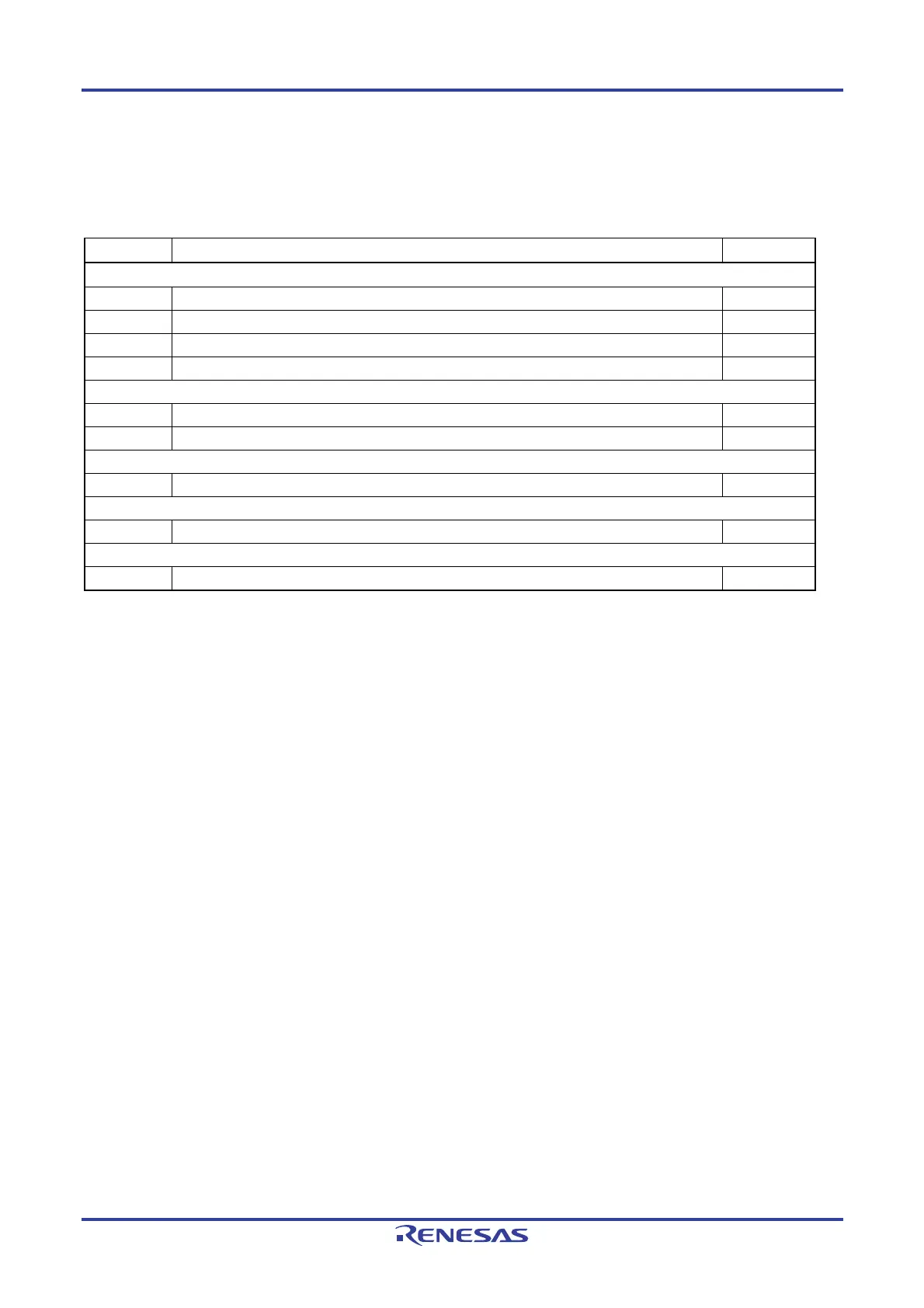

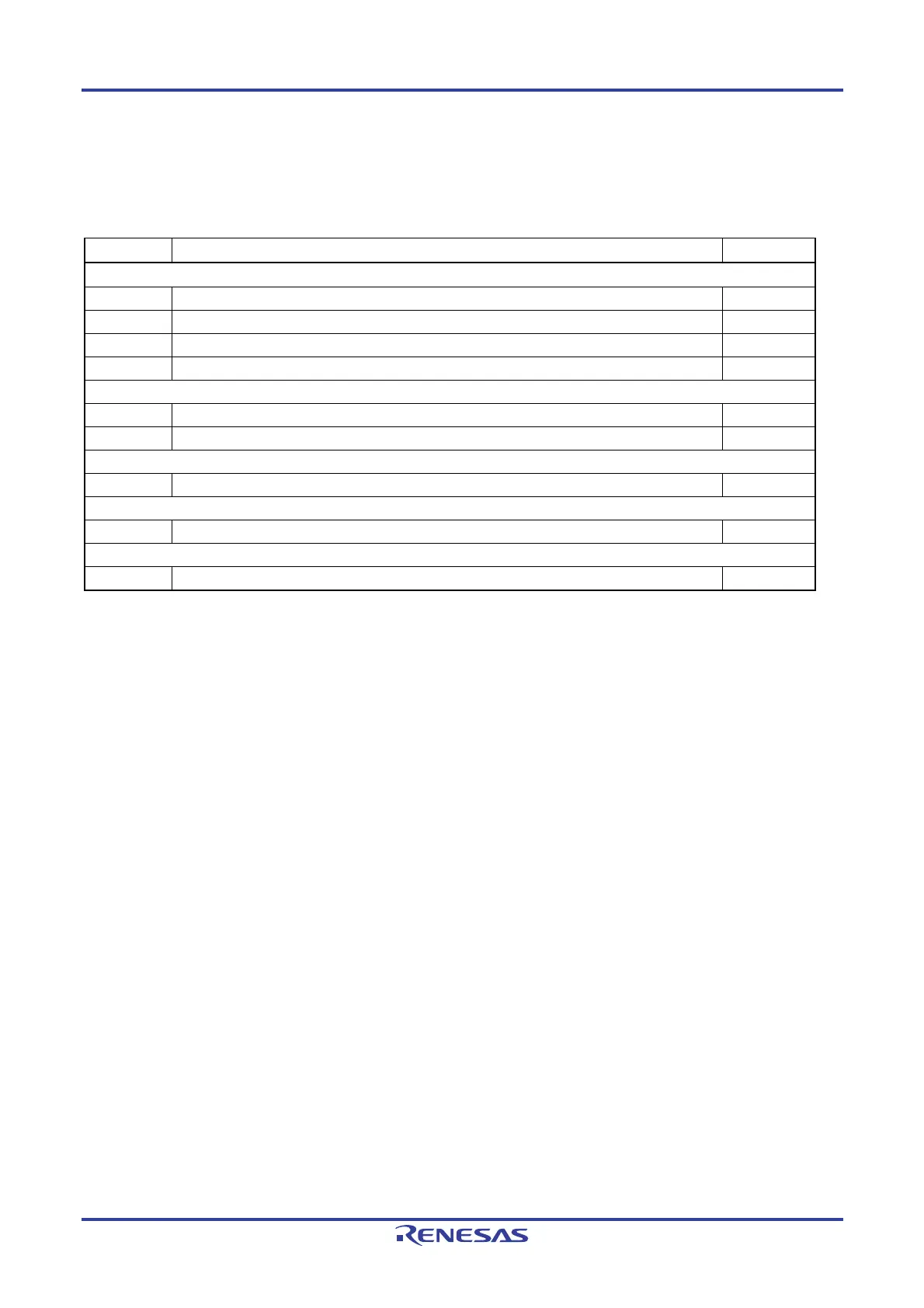

RL78/G10 APPENDIX A REVISION HISTORY

R01UH0384EJ0311 Rev. 3.11 608

Dec 22, 2016

APPENDIX A REVISION HISTORY

A.1 Major Revisions in This Edition

Page Description Classification

CHAPTER 3 CPU ARCHITECTURE

p.29 Correction of 3.1.2 Mirror area (a)

p.37 Addition of Note and correction of Table 3-4. SFR List (1/2) (c) (a)

p.38 Deletion of Processor mode control register in Table 3-4. SFR List (2/2) (a)

p.40 Addition of Note 1 to Table 3-5. Extended SFR (2nd SFR) List (1/2) (c)

CHAPTER 5 CLOCK GENERATOR

p.85 Correction of Figure 5-7. Format of Peripheral Enable Register 0 (PER0) (1/2) (a)

p.91 Correction of 5.4.3 Low-speed on-chip oscillator (a)

CHAPTER 11 COMPARATOR

p.269 Addition of description to 11.3.3 Comparator Filter Control Register (COMPFIR) (a)

CHAPTER 13 SERIAL INTERFACE IICA

p.424 Correction of Figure 13-9. Format of IICA Control Register 01 (IICCTL01) (1/2) (a)

CHAPTER 23 INSTRUCTION SET

p.580 Correction of Table 23-5. Operation List (13/17) (a)

Remark “Classification” in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note,

(d): Addition/change of package, part number, or management division, (e): Addition/change of related

documents

Loading...

Loading...