RL78/G10 CHAPTER 6 TIMER ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 168

Dec 22, 2016

6.8.3 Operation as frequency divider (only channels 0 and 3)

The timer array unit can be used as a frequency divider that divides a clock input to the TI0n pin and outputs the result

clock from the TO0n pin.

The divided clock frequency output from TO0n can be calculated by the following expression.

• When rising edge/falling edge is selected:

Divided clock frequency = Input clock frequency/{(Set value of TDR0n + 1) × 2}

• When both edges are selected:

Divided clock frequency ≅ Input clock frequency/(Set value of TDR0n + 1)

Timer count register 0n (TCR0n) operates as a down counter in the interval timer mode.

After the channel start trigger bit (TS0n) of timer channel start register 0 (TS0) is set to 1, the TCR0n register loads the

value of timer data register 0n (TDR0n) when the TI0n valid edge is detected.

If the MD00n bit of timer mode register 0n (TMR0n) is 0 at this time, INTTM0n is not output and TO0n is not toggled. If

the MD00n bit of timer mode register 0n (TMR0n) is 1, INTTM0n is output and TO0n is toggled.

After that, the TCR0n register counts down at the valid edge of the TI0n pin. When TCR0n = 0000H, it toggles TO0n.

At the same time, the TCR0n register loads the value of the TDR0n register again, and continues counting.

If detection of both the edges of the TI0n pin is selected, the duty factor error of the input clock affects the divided clock

period of the TO0n output.

The period of the TO0n output clock includes a sampling error of a maximum of one operating clock (f

MCK) period.

Clock period of TO0n output = Ideal TO0n output clock period ± Operating clock period (error)

The TDR0n register can be rewritten at any time. The new value of the TDR0n register becomes valid during the next

count period.

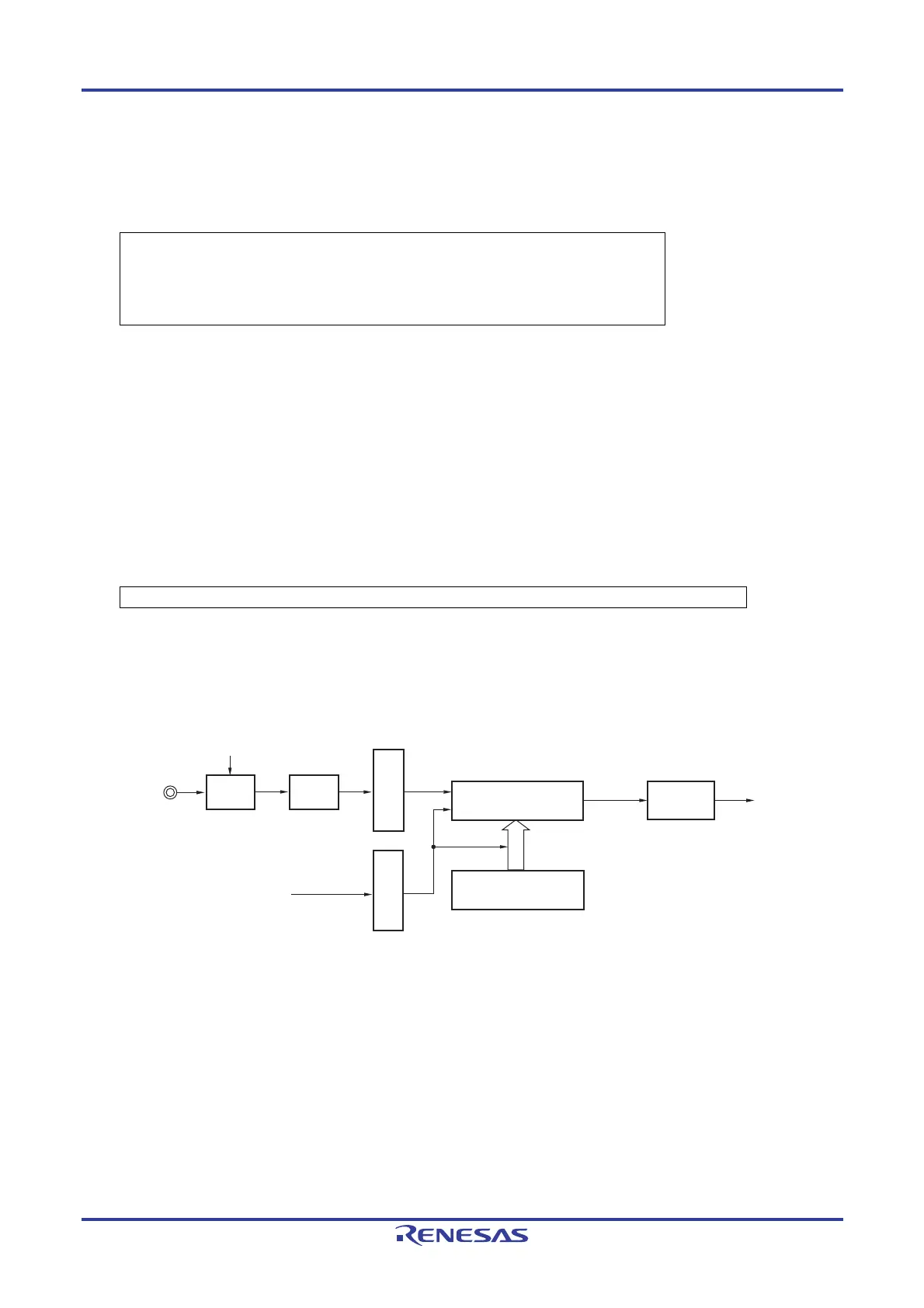

Figure 6-48. Block Diagram of Operation as Frequency Divider

TO0n pin

Output

controller

Clock selection

Trigger selection

Edge

detection

TI0n pin

TS0n

Timer counter

register 0n (TCR0n)

Timer data

register 0n (TDR0n)

Noise

filter

TNFEN0n

Remark n = 0, 3

Loading...

Loading...