RL78/G10 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0384EJ0311 Rev. 3.11 389

Dec 22, 2016

12.7.1 Address field transmission

Address field transmission is a transmission operation that first executes in I

2

C communication to identify the target for

transfer (slave). After a start condition is generated, an address (7 bits) and a transfer direction (1 bit) are transmitted in

one frame.

Simplified I

2

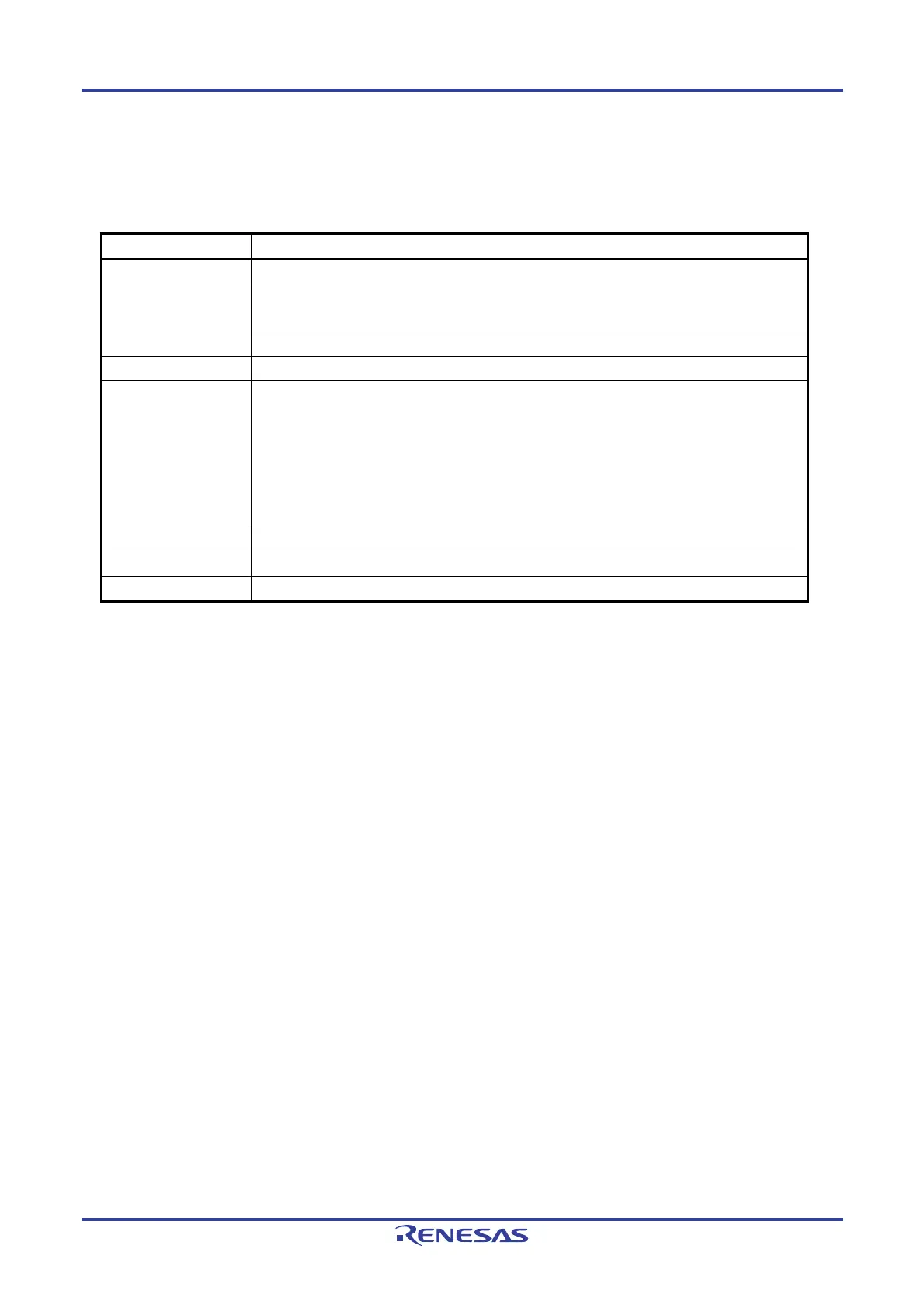

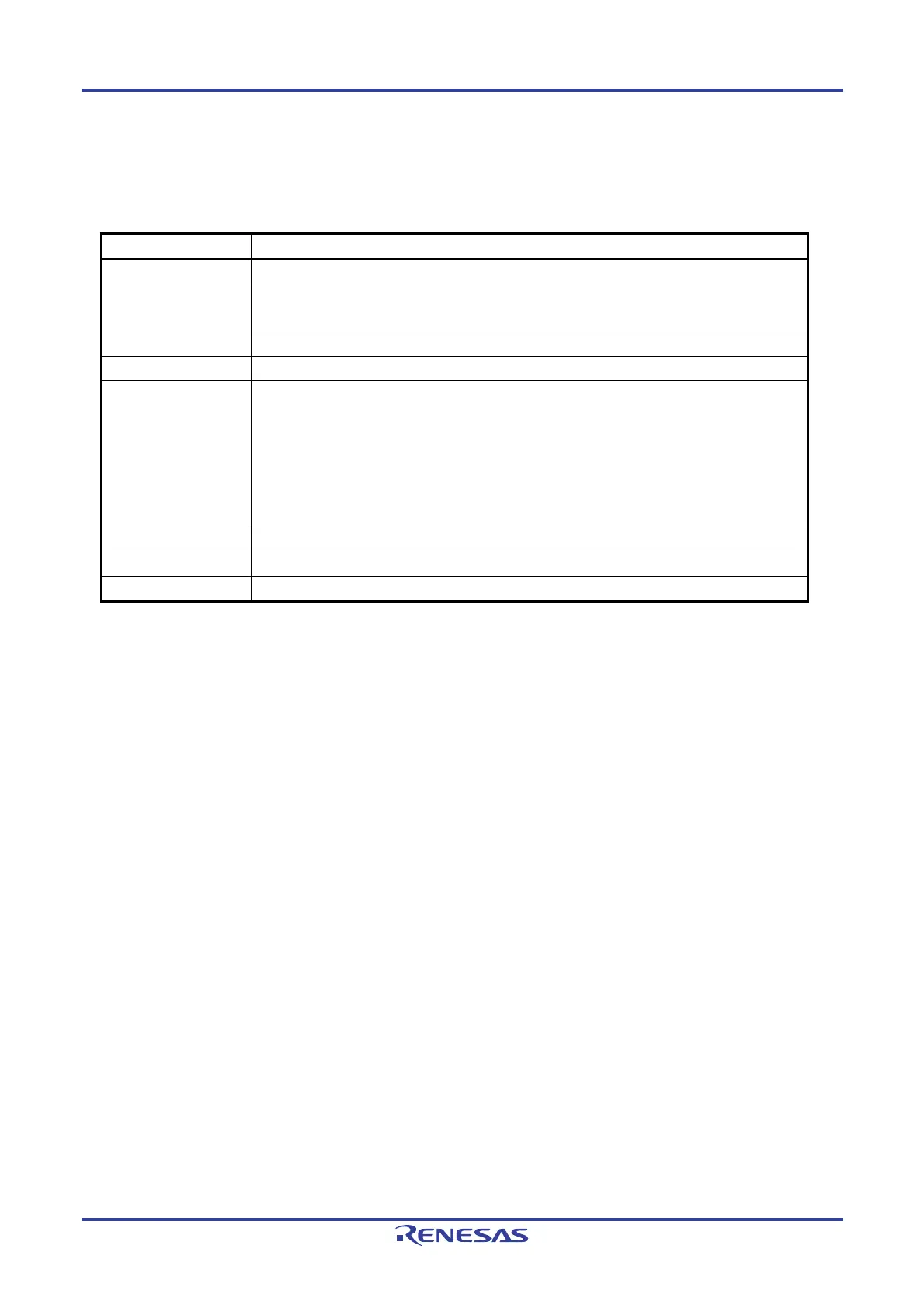

C IIC00

Target channel Channel 0 of SAU0

Pins used SCL00, SDA00

Note

Interrupt INTIIC00

Transfer end interrupt only (Setting the buffer empty interrupt is prohibited.)

Error detection flag ACK error detection flag (PEF0n)

Transfer data length

8 bits (transmitted with specifying the higher 7 bits as address and the least significant bit as

R/W control)

Transfer rate

Max. f

MCK/4 [Hz] (SDR0nH[7:1] = 1 or more) fMCK: Operation clock frequency of target channel

However, the following condition must be satisfied in each mode of I

2

C.

• Max. 400 kHz (fast mode)

• Max. 100 kHz (standard mode)

Data level Non-inversion output (default: high level)

Parity bit No parity bit

Stop bit Appending 1 bit (for ACK transmission/reception timing)

Data direction MSB first

Note To perform communication via simplified I

2

C, set the N-ch open-drain output (VDD tolerance) mode (POM01 = 1)

for the port output mode register (POM0) (see 4.3 Registers Controlling Port Function and 4.5 Register

Settings When an Alternate Function Is Used for details).

Remark n = 0

Loading...

Loading...